恾5-1. 柦椷偺堦斒宍幃

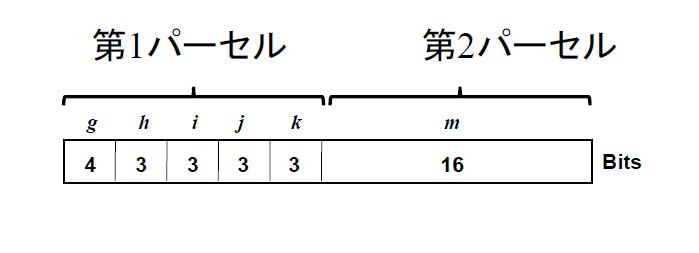

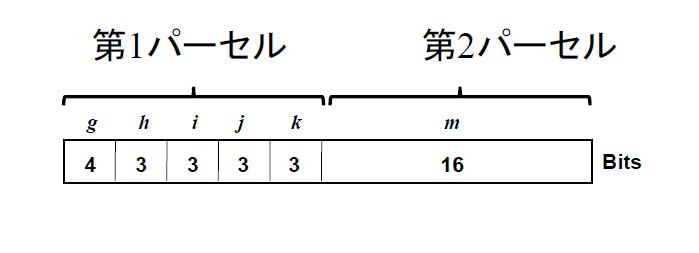

寁嶼婡拞偺奺柦椷偼1僷乕僙儖(16bit)柦椷偐丄2僷乕僙儖(32bit)柦椷偱偁傞丅 柦椷偼1儚乕僪偵偮偒丄4僷乕僙儖偑僷僢僋偝傟偰偄傞丅儚乕僪拞偺僷乕僙儖偼 嵍偐傜塃偵丄0偐傜3傑偱斣崋偑怳傜傟偰偍傝丄暘婒柦椷偱偳偺僷乕僙儖埵抲偱 傕傾僪儗僗偡傞偙偲偑偱偒傞丅2僷乕僙儖柦椷偼儚乕僪偺偳偺僷乕僙儖偐傜偱 傕巒傑傝丄儚乕僪嫬奅傪墇偊偰傕傛偄丅椺偊偽丄偁傞2僷乕僙儖柦椷偑偁傞儚乕 僪偺戞4僷乕僙儖偐傜巒傑傝丄師偺儚乕僪偺嵟弶偺僷乕僙儖偱廔傢傞丅儚乕僪 嫬奅偺偨傔偺僷僨傿儞僌偼晄梫偱偁傞丅恾5-1偼柦椷偺堦斒揑側宍幃傪帵偡丅

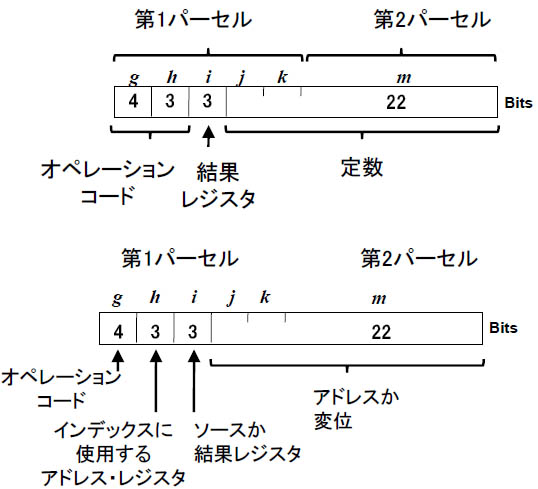

堦斒宍幃偵偼丄 僼傿乕儖僪傪堘偭偨巊梡傪偡傞 4偮偺僶儕僄乕僔儑儞偑偁傞; 2偮偺宍偼丄1僷乕僙儖宍幃偱偁傝丄 2偮偺宍偼丄2僷乕僙儖宍幃偱偁傞丅 偙傟傜偺4偮偺宍幃偼埲壓偱弎傋傞丅

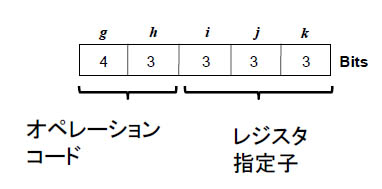

1僷乕僙儖柦椷偺懡偔偺嫟捠宍幃偼丄i,j,k僼傿乕儖僪傪偦傟偧傟僆儁儔儞僪偲 寢壥偺儗僕僗僞偺巜掕巕偲偡傞(恾5-2嶲徠)丅g,h僼傿乕儖僪偼僆儁儗乕僔儑儞丒 僐乕僪傪掕媊偡傞丅i僼傿乕儖僪偼寢壥儗僕僗僞傪巜掕偟丄j,k僼傿乕儖僪偼僆 儁儔儞僪丒儗僕僗僞傪巜掕偡傞丅偄偔偮偐偺柦椷偼丄1偮偐偦傟埲忋偺i,j,k 僼傿乕儖僪傪柍帇偡傞丅師偺宆偺柦椷偑丄偙偺宍幃傪巊梡偡傞丅

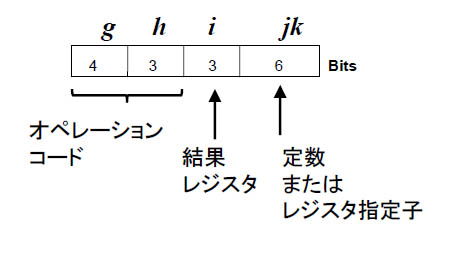

偄偔偮偐偺1僷乕僙儖柦椷偼j,k僼傿乕儖僪傪丄 寢崌偝傟偨6bit僼傿乕儖僪偲偟偰 巊梡偡傞(恾5-3嶲徠)丅 g,h僼傿乕儖僪偼 僆儁儗乕僔儑儞丒僐乕僪傪 帩偪丄i僼傿乕儖僪偼 堦斒揑偵僨僗僥傿僱乕僔儑儞丒儗僕僗僞 幆暿巕偱偁傞丅 寢崌偝傟偨j,k僼傿乕儖僪偼丄 堦斒揑偵掕悢,B偐T儗僕僗僞巜掕巕 傪帩偮丅 暘婒柦椷005偲 師偵帵偡宆偺柦椷偑丄 j,k僼傿乕儖僪偑寢崌偝傟偨 1僷乕僙儖柦椷宍幃傪巊梡偡傞丅

22bit懄抣偺偨傔偺柦椷偺宆偼丄 掕悢傪曐帩偡傞偨傔偵丄 寢崌偝傟偨j,k,m僼傿乕儖僪傪巊梡偡傞丅 7bit偺gh僼傿乕儖僪偼 僆儁儗乕僔儑儞丒僐乕僪傪 帩偪丄3bit偺i僼傿乕儖僪偑 寢壥儗僕僗僞傪巜掕偡傞丅 偙偺宍幃傪巊梡偡傞柦椷偼丄 22bit偺jkm掕悢傪A偐S儗僕僗僞偵 揮憲偡傞丅

僗僇儔丒儊儌儕揮憲偵巊梡偝傟傞 柦椷偺宆偼丄 傾僪儗僗曃嵎(僨傿僗僾儗僀僗儊儞僩 (廋忺偺僆僼僙僢僩))偺偨傔偵丄 22bit偺jkm僼傿乕儖僪傪 梫媮偡傞丅 偙偺柦椷宆偼丄 4bit偺g僼傿乕儖僪傪 柦椷僐乕僪偵巊梡偟丄 3bit偺h僼傿乕儖僪傪 僀儞僨僢僋僗丒儗僕僗僞偺巜掕偵丄 3bit偺i僼傿乕儖僪傪 僜乕僗偐寢壥儗僕僗僞偺巜掕偵 巊梡偡傞丅 (乽摿庩儗僕僗僞偺抣乿愡傪嶲徠)

恾5-4偼丄 j,k,m僼傿乕儖僪傪寢崌偟偨2僷乕僙儖 柦椷宍幃偺丄堦斒揑側2偮偺 揔梡傪帵偟偰偄傞丅

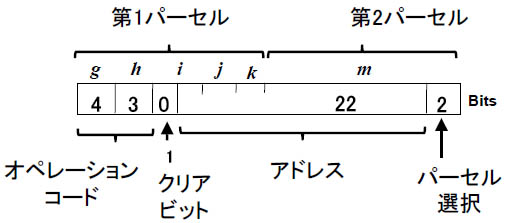

暘婒偺偨傔偺2僷乕僙儖柦椷宆(恾5-5)偼丄 偁傞柦椷僷乕僙儖傊 暘婒偡傞偺偨傔偺 24bit傾僪儗僗傪帩偮偨傔偵丄 寢崌偟偨i,j,k,m僼傿乕儖僪傪 巊梡偡傞丅 7bit僆儁儗乕僔儑儞丒僐乕僪(gh) 偵丄ijkm僼傿乕儖僪偑懕偔丅 i僼傿乕儖僪偺嵟忋埵價僢僩偼 0偱偁傞丅

24bit懄抣偺偨傔偺2僷乕僙儖 柦椷宆(恾5-6)偼丄 寢崌偟偨i,j,k,m僼傿乕儖僪傪 掕悢傪曐帩偡傞偨傔偵 巊梡偡傞丅 偙偺柦椷偺宆偼 4bit偺g僼傿乕儖僪傪 僆儁儗乕僔儑儞丒僐乕僪偵丄 3bit偺h僼傿乕儖僪傪寢壥傾僪儗僗 丒儗僕僗僞傪巜掕偡傞偺偵巊梡偡傞丅 i僼傿乕儖僪偺嵟忋埵價僢僩偼1偱偁傞丅

傕偟丄S0偲A0儗僕僗僞偑丄 柦椷偺j偐k僼傿乕儖僪偱 嶲徠偝傟偰偄偨傜丄 奺乆偺儗僕僗僞偺撪梕偼 巊梡偝傟側偄丅 偦偺戙傢傝丄摿暿側僆儁儔儞僪偑 惗惉偝傟傞丅 摿庩抣偼丄 A0偐S0傊偺梊栺偺懚嵼偵偼 柍撢拝偵棙梡壜擻偱偁傞 (偦偟偰丄偙偺働乕僗偱偼梊栺偼僠僃僢僋偝傟側偄) 傕偟丄S0偐A0偑i僼傿乕儖僪偱 僆儁儔儞僪偲偟偰巊梡偝傟偰偄偨傜丄 儗僕僗僞偺杮摉偺抣偑採嫙偝傟傞丅 師偺昞偑丄摿庩抣傪帵偡丅

| 僼傿乕儖僪 | 僆儁儔儞僪抣 |

|---|---|

| Ah, h=0 | 0 |

| Ai, i=0 | (A0) |

| Aj, j=0 | 0 |

| Ak, k=0 | 1 |

| Si, i=0 | (S0) |

| Sj, j=0 | 0 |

| Sk, k=0 | 2^63 |

柦椷偼 堦搙偵1僷乕僙儖偑 柦椷僶僢僼傽偐傜撉傑傟丄 師柦椷僷乕僙儖(NIP)儗僕僗僞傊 攝憲偝傟傞丅 捈慜偺柦椷偑敪峴偟偨傜丄 柦椷偼尰嵼柦椷僷乕僙儖(CIP) 儗僕僗僞傊搉偝傟傞丅 幚峴偵昁梫側婡擻偺幚峴偑 愭偵敪峴偝傟偨柦椷偲 徴撍柍偟偵壜擻偱偁傞偲偄偆傛偆側丄 忦審偑丄婡擻儐僯僢僩偲儗僕僗僞偱枮偨偝傟傞偲偒丄 CIP儗僕僗僞拞偺柦椷偑敪峴偝傟傞丅 CIP儗僕僗僞奜偺 柦椷僷乕僙儖偼丄嵟崅儗乕僩丄 1僋儘僢僋廃婜偛偲偵敪峴壜擻偱偁傞丅

幚峴帪娫(敪峴偐傜丄僨僗僥傿僱乕僔儑儞偺憖嶌儗僕僗僞傊僨乕僞偑撏偗傜傟 傞傑偱偺帪娫)偼柦椷000偐傜077傑偱屌掕偱偁傞丅偨偩偟丄儊儌儕嶲徠傪偡傞 傕偺(柦椷000,004, 暘婒柦椷005偐傜017傑偱偲丄僽儘僢僋揮憲柦椷034偐傜 037)傪彍偄偰丅僗僇儔丒儊儌儕柦椷100偐傜137偼丄壜曄挿帪娫偱姰椆偡傞丅 儀僋僩儖憖嶌柦椷140偐傜177偼丄柦椷偑儊儌儕丒僼僃僢僠偲僠僃僀儞偝傟偰偄 側偗傟偽屌掕帪娫偱姰椆偡傞丅

幚峴帪娫偼丄jk偱巜掕偝傟偨僙儅僼僅傪僥僗僩丒傾儞僪丒僙僢僩偡傞柦椷 0034jk偵傛偭偰塭嬁傪庴偗傞丅傕偟丄僙儅僼僅偑僙僢僩偝傟偰偄偨傜丄懠偺 CPU偑偦偺僙儅僼僅傪僋儕傾偡傞傑偱丄柦椷敪峴偼儂乕儖僪偝傟傞丅傕偟僙儅 僼僅偑僋儕傾偝傟偰偄偨傜丄柦椷偼敪峴偟丄僙儅僼僅傪僙僢僩偡傞丅僋儔僗僞 拞偺慡CPU偑僥僗僩丒傾儞僪丒僙僢僩偱敪峴偑儂乕儖僪偝傟偨傜丄(儌僯僞丒儌乕 僪偱側偗傟偽) 岎姺僷僢働乕僕拞偺僼儔僌偑僙僢僩偝傟丄岎姺偑敪惗偡傞丅僥 僗僩丒傾儞僪丒僙僢僩柦椷偑CIP儗僕僗僞撪偱儂乕儖僪偺婜娫拞偵妱傝崬傒偑 敪惗偟偨傜丄岎姺僷僢働乕僕拞偺僼儔僌偼僙僢僩偝傟丄CIP偲NIP儗僕僗僞偼僋 儕傾偝傟丄P儗僕僗僞偑僥僗僩丒傾儞僪丒僙僢僩柦椷傪巜偡傛偆偵偟側偑傜丄 岎姺偑敪惗偡傞丅

2僷乕僙儖柦椷偺2斣栚偺僷乕僙儖偺NIP儗僕僗僞傊偺搊榐偼僽儘僢僋偝傟丄 NIP偼嬻偵側傞丅偦偺戙傢傝丄偦偺僷乕僙儖偼掅懁柦椷僷乕僙儖(Lower Instruction Parcel:LIP) 儗僕僗僞傊憲傜傟傞丅NIP拞偺楇(壖憐戞擇僷乕僙儖) 偑CIP傊憲傜傟丄壗傕偟側偄柦椷偲偟偰敪峴偡傞丅

Ah,Aj,Ak,Sj,Sk偺偨傔偺柦椷偱摿庩儗僕僗僞抣(A0偐S0)偑慖戰偝傟偨帪丄捠忢 偺乽僆儁儔儞僪偑弨旛偱偒傞傑偱敪峴偑儂乕儖僪偡傞乿忦審偼揔梡偝傟側偄丅 偙傟傜偺抣偼丄忢偵懄嵗偵棙梡偱偒傞丅

偙偺愡偵偼丄屄乆偺柦椷傗娭楢偟偨柦椷偺僌儖乕僾偵偮偄偰偺嵶偐偄忣曬偑偁 傞丅奺柦椷偼丄CAL(Cray傾僙儞僽儕尵岅)暥朄宍幃丄奺柦椷偺梫栺婰弎丄gh僼傿乕 儖僪偱掕媊偝傟偨敧恑僐乕僪楍偺忣曬偐傜惉傞敔宆偺忣曬偐傜巒傑傞丅宍幃拞 偺m偺弌尰偼丄柦椷偑2偮偺僷乕僙儖偐傜惉傞偙偲傪帵偡丅

堷偒懕偔敔宆忣曬偼丄敪峴儂乕儖僪忦審偺儕僗僩丄幚峴帪娫丄摿庩側働乕僗傪 娷傓丄柦椷傗柦椷払偺傕偭偲徻偟偄婰弎偑偁傞丅敪峴儂乕儖僪忦審偼丄忦審偑 堦抳偡傞傑偱柦椷偺敪峴傪抶傜偣傞忦審傪嶲徠偡傞丅

柦椷敪峴帪娫偼丄師偺傛偆側傕偺偱偁傞丄傕偟偁傞柦椷偑僋儘僢僋廃婜n

(CP n)偱敪峴偟偨偺偱偁傟偽丄師偺柦椷偼丄偦傟偺敪峴忦審偑堦抳偟偨傜

CP n+敪峴帪娫(拲+)

偱敪峴偡傞丅

(拲+ : 慜偺柦椷偑敪峴偟偨屻)

師偺摿庩暥帤偼丄婰崋婡夿柦椷偺僆儁儔儞僪丒僼傿乕儖僪婰弎偵尰傟丄幚峴偝 傟傞憖嶌傪寛掕偡傞傾僙儞僽儔偱巊梡偝傟傞丅

柦椷拞偱偼丄埲壓偺暥帤偺慜偵儗僕僗僞巜掕巕偑抲偐傟傞丅偦傟傜偼傾僙儞僽 儔偱摿暿側堄枴傪帩偮丅

| 柦椷000 | ||||||

|---|---|---|---|---|---|---|

|

柦椷000偼丄僄儔乕忬懺偲偟偰埖傢傟丄岎姺僔乕働儞僗偑婲摦偡傞丅柦椷僶僢 僼傽偺撪梕偼丄岎姺僔乕働儞僗偵傛傝攋婞偝傟傞丅柦椷000偼丄岆偭偰婰弎偝 傟偨儊儌儕偺枹巊梡椞堟(傕偟丄儊儌儕偑0偱杽傔偮偔偝傟偰偄傟偽)傗丄僨乕 僞椞堟(傕偟僨乕僞偑丄惓偺惍悢丄塃媗ASCII丄晜摦彫悢揰0側傜偽) 傊暘婒偡 傞僾儘僌儔儉偺幚峴傪掆巭偡傞丅傕偟儌僯僞儌乕僪偑桳岠偱側偗傟偽丄F儗僕 僗僞拞偺ErrorExit僼儔僌偑僙僢僩偝傟傞丅偙偺柦椷偺慜偵敪峴偝傟偨慡柦椷 偼姰椆偡傞傑偱幚峴偝傟傞丅愭偵敪峴偝傟偨柦椷偺寢壥偑僆儁儗乕僥傿儞僌丒 儗僕僗僞(憖嶌儗僕僗僞)偵摓拝偟偨帪丄XA儗僕僗僞偺撪梕偵傛偭偰巜掕偝傟偨丄 岎姺僷僢働乕僕偱岎姺偑婲摦偡傞丅岎姺僔乕働儞僗廔椆帪偵丄岎姺拞偵奿擺偝 傟傞僾儘僌儔儉偺傾僪儗僗偼P儗僕僗僞偺撪梕傪1恑傔偨傕偺偱偁傞(偮傑傝丄 ErrorExit柦椷偵堷偒懕偔柦椷偺傾僪儗僗偱偁傞)丅

儂乕儖僪敪峴忦審: A,S,V儗僕僗僞偺偳傟偐偑梊栺嵪傒

幚峴帪娫: 柦椷敪峴, 40CP; 偙偺帪娫偵偼岎姺僔乕働儞僗(24CP) 偲僼僃僢僠憖嶌(16CP)傪娷傓

摿庩忦審: 柍偟

| 柦椷 0010 - 0013 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷0010偐傜0013偼丄儌僯僞儌乕僪偺摿尃偱僆儁儗乕僥傿儞僌丒僔僗僥儉傪曋 棙側憖嶌偑採嫙偝傟偰偄傞丅婡擻偼i巜掕巕偱慖戰偝傟傞丅傕偟儌僯僞儌乕僪丒 價僢僩偑僙僢僩偝傟偰偄側偗傟偽丄柦椷偼僷僗(pass)柦椷偲摨條偵埖傢傟傞丅

i巜掕巕偑0,1,2偺偳傟偐偺帪丄柦椷偼IO僠儍儞僱儖偺憖嶌傪惂屼偡傞丅奺僠儍 儞僱儖偼僠儍儞僱儖偺傾僋僥傿價僥傿傪巜掕偡傞偺偵丄2偮偺儗僕僗僞傪帩偭 偰偄傞丅僠儍儞僱儖偺CA儗僕僗僞偼丄尰嵼偺(僇儗儞僩)僠儍儞僱儖丒儚乕僪偺 傾僪儗僗傪帩偭偰偄傞丅CL儗僕僗僞偼丄尷奅(儕儈僢僩) 傾僪儗僗傪巜掕偡傞丅 僠儍儞僱儖偺僾儘僌儔儈儞僌偱偼丄嵟弶偵CL儗僕僗僞傪弶婜壔偟丄偦傟偐傜CA 儗僕僗僞傪僙僢僩偟偰丄僠儍儞僱儖傪傾僋僥傿儀乕僩偡傞丅CA偑CL偵側傞傑偱 揮憲偑懕偔丅(CA)偑(CL)偲摨堦偵側偭偨帪丄嵟弶偺(CA)偐傜(CL)-1傑偱偺儚乕 僪偺揮憲偑姰椆偡傞丅j巜掕巕偑0偱偁傞偐Aj偺壓4價僢僩偑7(敧恑)傛傝彫偝偄 偲偒丄婡擻偼僷僗(pass)柦椷偲摨條偵幚峴偝傟傞丅惓偟偄僠儍儞僱儖斣崋偼 7-17(敧恑)偱偁傞丅k巜掕巕偑0偺帪丄CA偐CL偼1偵僙僢僩偝傟傞丅

i巜掕巕偑3偺帪丄柦椷偼(Aj)偺2^11價僢僩偐傜2^4傪XA儗僕僗僞傊揮憲偡傞丅j 巜掕巕偑0偺帪丄XA儗僕僗僞偼僋儕傾偝傟傞丅

柦椷0012j0偼僨僶僀僗丒儅僗僞丒僋儕傾傪僋儕傾偡傞偨傔偵巊梡偝傟傞丅柦椷 0012偱偼丄傕偟弌椡僠儍儞僱儖梡偺k巜掕巕偑1側傜偽丄儅僗僞丒僋儕傾偑僙僢 僩偝傟丄傕偟擖椡僠儍儞僱儖梡偺k巜掕巕偑1側傜偽丄儗僨傿丒僼儔僌偑僋儕傾 偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

CPU娫偵偼僴乕僪僂僃傾丒僀儞僞乕儘僢僋偼傑偭偨偔柍偄丅2偮偺CPU偱偙傟傜 偺柦椷傪摨帪偵敪峴偡傞偙偲偑壜擻偵側偭偰偄傞丅偟偐偟丄偦傟偵傛傝丄寛掕 偱偒側偄寢壥偑敪惗偡傞丅

僜僼僩僂僃傾偼丄儌僯僞丒儌乕僪偺娫丄堦帪偵丄偨偩堦偮偺CPU偑IO僒乕價僗

傪峴偆傛偆偵曐徹偟側偗傟偽側傜側偄丅

-------

pp.5-10

| 柦椷0014 | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷0014偼丄幚帪娫偲僾儘僌儔儉壜擻僋儘僢僋傪娗棟偡傞偨傔偺摿暿側婡擻傪 幚峴偟丄妱傝崬傒梫媮偲僋儔僗僞斣崋憖嶌傪庢傝埖偆丅柦椷0014偼儌僯僞丒儌乕 僪偱偺摿尃偱偁傝丄儌僯僞丒儌乕僪丒價僢僩偑僙僢僩偝傟偰偄側偄偲偒偵偼丄 僷僗柦椷偲偟偰埖傢傟傞丅

k巜掕巕偑0偺帪偼丄柦椷偼Sj儗僕僗僞偺撪梕傪RTC儗僕僗僞偵擖傟傞丅j巜掕巕 偑0偐(Sj)=0側傜偽丄RTC儗僕僗僞偼僋儕傾偝傟傞丅

k巜掕巕偑1偺帪丄柦椷偼懠偺CPU撪偺撪晹CPU妱傝崬傒梫媮傪僙僢僩偡傞丅傕偟丄 懠偺CPU偑儌僯僞丒儌乕僪偱側偗傟偽丄F儗僕僗僞撪偺乽撪晹CPU偐傜偺妱傝崬 傒(ICP)僼儔僌乿偑僙僢僩偝傟丄妱傝崬傒偑堷偒婲偙偝傟傞丅梫媮偼丄庴偗庢偭 偨CPU偑柦椷001402傪敪峴偡傞偙偲偵傛偭偰丄僋儕傾偝傟傞傑偱丄巆傞丅

k巜掕巕偑2偺帪丄柦椷偼丄懠偺CPU偵傛偭偰僙僢僩偝傟偨撪晹CPU妱傝崬傒梫媮 傪僋儕傾偡傞丅

k巜掕巕偑3偺帪丄柦椷偼丄師偺僋儔僗僞慖戰傪峴偆偨傔偵丄僋儔僗僞斣崋傪j 偵偡傞:

k巜掕巕偑4偺帪丄柦椷偼Sj儗僕僗僞偐傜壓32價僢僩傪II儗僕僗僞偲ICD僇僂儞 僞偺椉曽傊儘乕僪偡傞丅j巜掕巕偑0偐(Sj)=0偺帪丄II偲ICD偼僋儕傾偝傟傞丅

k巜掕巕偑5偺帪丄傕偟梫媮偑ICD僇僂儞僩僟僂儞偑0偵側偭偨偙偲偵傛偭偰丄愭 傫偠偰僾儘僌儔儅僽儖丒僋儘僢僋妱傝崬傒梫媮偑僙僢僩偝傟偰偄偨応崌丄柦椷 偼丄梫媮傪僋儕傾偡傞丅

k巜掕巕偑6偺帪丄僾儘僌儔儅僽儖丒僋儘僢僋妱傝崬傒梫媮偺孞傝曉偟傪僀僱乕 僽儖偡傞丅孞傝曉偟棪偼II儗僕僗僞拞偺抣偱寛掕偝傟傞丅

k巜掕巕偑7偺帪丄僾儘僌儔儅僽儖丒僋儘僢僋妱傝崬傒梫媮偺孞傝曉偟傪丄僨傿 僗僄乕僽儖偡傞丅柦椷001406偑幚峴偝傟傞偲丄偙偺梫媮偼僀僱乕僽儖偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷0015 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||

| 拲* 尰嵼偼僒億乕僩偝傟偰偄側偄 |

偙傟傜偺柦椷偼偡傋偰儌僯僞丒儌乕僪偵摿尃偑嫋偝傟偰偄傞丅

柦椷0015j0偼丄惈擻僇僂儞僞偵傛偭偰娔帇偝傟傞僴乕僪僂僃傾偵娭偡傞僀儀儞 僩偺4偮偺僌儖乕僾偆偪偺1偮傪慖戰偡傞丅惈擻娔帇偑偳偺傛偆偵惉偟悑偘傜傟 偰偄傞偐偺婰弎偼丄晅榐C 傪嶲徠丅

柦椷001501偐傜001531偼丄SECDEC偵娭學偡傞儌僕儏乕儖偺憖嶌偺僠僃僢僋偲丄 僄儔乕偺専弌偲掶惓偺専徹偵巊梡偝傟傞丅儊僀儞僼儗乕儉偺惂屼僷僱儖偺乽儊 儞僥僫儞僗丒儌乕僪乿僗僀僢僠偼丄偙傟傜偺柦椷偺幚峴拞偼ON偵擖偭偰偄側偗 傟偽側傜側偄丅偦偆偱側偗傟偽丄柦椷偼no-op偵側傞丅SECDEC儊儞僥僫儞僗丒 儌乕僪婡擻偺婰弎偵偮偄偰偼丄晅榐D傪嶲徠丅

柦椷001501偲001521偼僠僃僢僋丒價僢僩儊儌儕婰壇偺専徹偵巊梡偝傟傞丅柦椷 001501偼丄堷偒懕偔偡傋偰偺儊儌儕撉傒弌偟(僼僃僢僠偲I/O傕娷傓)偺丄CPU僷 僗偺偄偔偮偐偺僨乕僞丒價僢僩傪丄SECDED梡偺8僠僃僢僋丒價僢僩偲抲偒姺偊 傞傛偆偵偡傞丅柦椷001521偼丄堷偒懕偔偡傋偰偺儊儌儕彂偒崬傒偺丄偄偔偮偐 偺僨乕僞丒價僢僩傪丄SECDED梡偺8僠僃僢僋丒價僢僩偲抲偒姺偊傞傛偆偵偡傞丅

柦椷001511偲001531偼丄僄儔乕専弌掶惓偺専徹偵巊梡偝傟傞丅柦椷001511偼丄 恌抐僠僃僢僋丒僶僀僩傪S1偺忋埵8bit偵儘乕僪偡傞丅柦椷001531偼丄堷偒懕偔 偡傋偰偺儊儌儕彂偒崬傒偺丄彂偒崬傕偆偲偟偰偄傞SECDED梡偺8僠僃僢僋丒價僢 僩傪8bit偺恌抐僠僃僢僋丒僶僀僩偲抲偒姺偊傞傛偆偵偡傞丅

pp 5-13

| 柦椷0020 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| |||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷00200k偼丄 Ak偺撪梕偱巜掕偝傟傞抣傪 VL儗僕僗僞傊擖傟傞丅 (Ak)偺壓埵6bit偑VL儗僕僗僞偵擖傞丅 傕偟丅(Ak)偺壓埵6bit偑0側傜偽丄 VL偺7斣栚偺價僢僩偑僙僢僩偝傟傞丅 (***栿拲:(Ak)偺壓6bit偑0偺帪偼丄64傪昞偟丄 VL儗僕僗僞偵偼丄64偑擖傞***) 椺偊偽丄傕偟(Ak)=0傑偨偼100(敧恑)偺攞悢 偱偁偭偨傜丄VL=100(敧恑)偱偁傞丅 VL偺撪梕偼偄偮傕1偐傜100(敧恑)偺娫偱偁傞丅 柦椷002000偼丄抣1傪VL儗僕僗僞偵憲傞丅 儂乕儖僪敪峴忦審:Ak偑梊栺嵪傒 (A0傪彍偔) 幚峴帪娫: 柦椷敪峴, 1CP VL儗僕僗僞丒儗僨傿, 1CP 摿庩忦審: 嵟戝儀僋僩儖挿偼64. (Ak)=1 偲偡傞丄傕偟 k=0 側傜. (VL)=100(敧恑) 偲偡傞丄傕偟 k亗0 偐偮 (Ak)=0偐(Ak)偑100(敧恑)偺攞悢偱偁傟偽. pp 5-14

| 柦椷0021 - 0027 | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷002100偼丄M儗僕僗僞拞偺晜摦彫悢揰儌乕僪(Floating-point Mode)僼儔僌 傪丄僙僢僩偡傞丅柦椷002200偼丄M儗僕僗僞拞偺晜摦彫悢揰儌乕僪 (Floating-point Mode)僼儔僌傪丄僋儕傾偡傞丅2偮偺柦椷偼僼儔僌偺慜偺忬懺 傪僠僃僢僋偟側偄丅晜摦彫悢揰儌乕僪(Floating-point Mode)僼儔僌偑僙僢僩 偝傟偰偄傞偲偒丄4復偱弎傋偨晜摦彫悢揰斖埻僄儔乕偱偺妱傝崬傒傪嫋壜偡傞丅 偙傟傜偺柦椷偺偳偪傜偐偑敪峴偡傞偲偒丄摨帪偵丄晜摦彫悢揰僄儔乕丒僗僥乕 僞僗丒僼儔僌偑僋儕傾偝傟傞丅

柦椷002300偼丄M儗僕僗僞拞偺僆儁儔儞僪斖埻儌乕僪(Operand Range Mode)僼 儔僌傪僙僢僩偡傞丅柦椷002400偼丄M儗僕僗僞拞偺僆儁儔儞僪斖埻儌乕僪丒僼 儔僌傪僋儕傾偡傞丅2偮偺柦椷偼僼儔僌偺慜偺忬懺傪僠僃僢僋偟側偄丅僆儁儔 儞僪斖埻儌乕僪(Operand Range Mode)僼儔僌偑僙僢僩偝傟偰偄傞偲偒丄3復偱 弎傋偨丄僆儁儔儞僪(傾僪儗僗)斖埻僄儔乕偱偺妱傝崬傒傪嫋壜偡傞丅

柦椷002500偼憃曽岦儊儌儕揮憲傪嬛巭偡傞丅柦椷002600偼憃曽岦儊儌儕揮憲傪 嫋壜偡傞丅憃曽岦儊儌儕儌乕僪偱偼丄僽儘僢僋丒儕乕僪偲僽儘僢僋丒儔僀僩偼丄 暲峴偵摦嶌偱偒傞丅傕偟憃曽岦儊儌儕儌乕僪偑嬛巭偝傟偰偄傞偲丄暋悢偺僽儘僢 僋丒儕乕僪偩偗偑暲峴偵摦嶌偱偒傞丅

柦椷002700偼丄柦椷傪敪峴拞偺CPU撪偺偡傋偰偺儊儌儕嶲徠偺姰椆傪曐徹偡傞丅

柦椷002700偼丄偙偺柦椷偺慜偺偡傋偰偺儊儌儕嶲徠偑幚峴僗僥乕僕偵偁傞偆偪

偼丄敪峴偟側偄丅嶲徠偺姰椆偼丄慡晹偺崌寁帪娫屻偵敪惗偡傞丅椺偊偽丄CPU

偵傛偭偰CMR柦椷偑敪峴偝傟偨僗僩傾偵傛傞僨乕僞傪丄儘乕僪偡傞偲偒丄

002700偼CMR柦椷偺屻偵敪峴偝傟偨儘乕僪偑丄峏怴偝傟偨僨乕僞傪庴偗庢傞偙

偲傪曐徹偡傞丅

(***栿拲: 偁傞斣抧偵丄僗僩傾柦椷傪敪峴偟丄CMR傪敪峴偣偢偵丄摨偠斣抧傪

撉傒崬傓偲僗僩傾慜偺屆偄僨乕僞傪撉傓偙偲偑偁傞丅CMR 偱僗僩傾偺姰椆傪懸偭

偰偐傜丄儘乕僪傪敪峴偡傞偲丄昁偢峏怴屻偺僨乕僞傪撉傒崬傒帠偑偱偒傞***)

僾儘僙僢僒娫偺儊儌儕嶲徠偺摨婜偼丄僙儅僼僅柦椷偲偙偺柦椷傪楢寢偡傞偙偲

偵傛偭偰峴傢傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷0030, 0034, 0036,0037 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷0030j0偼丄VM儗僕僗僞偵Sj偺撪梕傪擖傟傞丅柦椷003000偱j巜掕巕偑0偺帪丄 VM儗僕僗僞偼僋儕傾偝傟傞丅偙傟傜偺柦椷偼丄儀僋僩儖丒儅乕僕柦椷(146偲 147)偲慻傒崌傢偣偰巊梡偝傟傞丅VM偺撪梕偵傛偭偰丄儀僋僩儖丒儅乕僕憖嶌偑 幚峴偝傟傞丅

柦椷0034jk偼丄jk偱巜掕偝傟傞僙儅僼僅偺僥僗僩丒傾儞僪丒僙僢僩偱偁傞丅傕 偟僙儅僼僅偑僙僢僩偝傟偰偄偨傜丄懠偺CPU偑僙儅僼僅傪僋儕傾偡傞傑偱敪峴 偑儂乕儖僪偝傟傞丅傕偟僙儅僼僅偑僋儕傾偝傟偰偄偨傜丄柦椷偼敪峴偟丄僙儅 僼僅偼僙僢僩偝傟傞丅

傕偟僋儔僗僞撪偺慡CPU偑僥僗僩丒傾儞僪丒僙僢僩偺敪峴偱儂乕儖僪偝傟偰偄 偨傜丄岎姺僷僢働乕僕拞偺DL僼儔僌偑僙僢僩偝傟(儌僯僞丒儌乕僪偱側偄偲偟偰)丄 岎姺偑敪惗偡傞丅

CIP儗僕僗僞撪偱僥僗僩丒傾儞僪丒僙僢僩柦椷偑儂乕儖僪拞偵丄妱傝崬傒偑敪 惗偟偨傜丄岎姺僷僢働乕僕拞偺WS僼儔僌偑僙僢僩偝傟丄CIP偲NIP儗僕僗僞偑僋 儕傾偝傟丄偦偟偰丄僥僗僩丒傾儞僪丒僙僢僩柦椷傪巜偟偰偄傞P儗僕僗僞傪帩偭 偨岎姺偑敪惗偡傞丅SM儗僕僗僞偼32bit偱偁傝丄SM0偼嵟忋埵價僢僩偱偁傞丅

柦椷0036jk偼jk偱巜掕偝傟傞僙儅僼僅傪僋儕傾偡傞丅

柦椷0037jk偼jk偱巜掕偝傟傞僙儅僼僅傪僙僢僩偡傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷004 | ||||||

|---|---|---|---|---|---|---|

|

柦椷004偼丄柦椷僶僢僼傽偺撪梕傪幪偰傞岎姺僔乕働儞僗傪敪惗偡傞丅傕偟儌 僯僞丒儌乕僪偑桳岠偱側偗傟偽丄F儗僕僗僞拞偺惓忢廔椆(Normal Exit)僼儔僌 偑僙僢僩偝傟傞丅偙偺柦椷偺慜偵敪峴偝傟偨偡傋偰偺柦椷偼丄姰椆傑偱憱峴偝 偣傜傟傞; 偮傑傝丄愭棫偭偰敪峴偝傟偨柦椷偺慡寢壥偑憖嶌儗僕僗僞偵摓拝偟 偨偲偒偵丄XA儗僕僗僞偺撪梕偱巜掕偝傟傞岎姺僷僢働乕僕傊偺丄岎姺僔乕働儞 僗偑婲摦偝傟傞丅岎姺僷僢働乕僕偵奿擺偝傟傞僾儘僌儔儉丒傾僪儗僗偼丄EX (惓忢廔椆)柦椷偺傾僪儗僗偐傜丄1恑傫偱偄傞丅柦椷004偼儐乕僓丒僾儘僌儔儉 偐傜儌僯僞梫媮傪敪峴偡傞偺偵巊梡偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷005 | ||||||

|---|---|---|---|---|---|---|

|

柦椷05 偼丄P儗僕僗僞傪丄Bjk偺撪梕偱偁傞24bit偺僷乕僙儖丒傾僪儗僗偵僙僢 僩偟丄幚峴傪堷偒懕偒偦偺傾僪儗僗偐傜峴偆傛偆偵偡傞丅偙偺柦椷偼丄僒僽儖乕 僠儞偐傜偺儕僞乕儞偵巊梡偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷006 | ||||||

|---|---|---|---|---|---|---|

|

2僷乕僙儖柦椷006偼丄P儗僕僗僞傪丄ijkm僼傿乕儖僪偺壓埵24bit偱巜掕偝傟傞 僷乕僙儖丒傾僪儗僗偵僙僢僩偡傞丅幚峴偼偦偺傾僪儗僗偐傜堷偒懕偔丅ijkm 僼傿乕儖僪偺忋埵價僢僩偼柍帇偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷007 | ||||||

|---|---|---|---|---|---|---|

|

2僷乕僙儖柦椷007偼丄B00偵丄柦椷偺2僷乕僙儖栚偵懕偔僷乕僙儖偺傾僪儗僗傪 僙僢僩偡傞丅偦偟偰丄P儗僕僗僞偼丄ijkm僼傿乕儖僪偺壓埵24bit偱巜掕偝傟傞 僷乕僙儖丒傾僪儗僗偵僙僢僩偝傟傞丅幚峴偼偦偺傾僪儗僗偐傜堷偒懕偔丅ijkm 僼傿乕儖僪偺忋埵價僢僩偼柍帇偝傟傞丅

偙偺柦椷偼僒僽儖乕僠儞丒僐乕儖偺栠傝偺儕儞僋傪採嫙偡傞丅僒僽儖乕僠儞偵 偼儕僞乕儞丒僕儍儞僾傪捠偟偰擖傞丅

僒僽儖乕僠儞偼丄B00儗僕僗僞偺撪梕傊偺暘婒傪幚峴偡傞偙偲偵傛偭偰丄屇傃 弌偟尦偺丄屇傃弌偟偵堷偒懕偔柦椷偵栠傞偙偲偑偱偒傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷010-013 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

010偐傜013偺2僷乕僙儖柦椷偼丄h僼傿乕儖僪偱巜掕偝傟傞忦審偱A0偺撪梕傪僥 僗僩偡傞丅忦審偑枮偨偝傟偨傜丄P儗僕僗僞偼丄ijkm僼傿乕儖僪偺壓埵24bit偱 巜掕偝傟傞僷乕僙儖丒傾僪儗僗偵僙僢僩偝傟丄幚峴偼偦偺傾僪儗僗偐傜堷偒懕 偔丅ijkm僼傿乕儖僪偺忋埵價僢僩偼0偱側偗傟偽側傜側偄丅忦審偑枮偨偝傟側 偄帪偼丄幚峴偼丄暘婒柦椷偺屻偵懕偔柦椷偐傜堷偒懕偔丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

-------

拲堄

僼僃僢僠偑敪惗偟偨応崌丄

儊儌儕徴撍偼抶墑傪惗偠傞偱偁傠偆

---

摿庩忦審:

| 柦椷014-017 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

014偐傜017偺2僷乕僙儖柦椷偼丄h僼傿乕儖僪偱巜掕偝傟傞忦審偱S0偺撪梕傪僥 僗僩偡傞丅忦審偑枮偨偝傟偨傜丄P儗僕僗僞偼丄ijkm僼傿乕儖僪偺壓埵24bit偱 巜掕偝傟傞僷乕僙儖丒傾僪儗僗偵僙僢僩偝傟丄幚峴偼偦偺傾僪儗僗偐傜堷偒懕 偔丅ijkm僼傿乕儖僪偺忋埵價僢僩偼0偱側偗傟偽側傜側偄丅忦審偑枮偨偝傟側 偄帪偼丄幚峴偼丄暘婒柦椷偺屻偵懕偔柦椷偐傜堷偒懕偔丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

-------

拲堄

僼僃僢僠偑敪惗偟偨応崌丄

儊儌儕徴撍偼抶墑傪惗偠傞偱偁傠偆

---

摿庩忦審:

| 柦椷020-021 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

|

2僷乕僙儖柦椷020偼丄jkm僼傿乕儖僪偺22bit偲嵟忋埵2bit偺0偱偱偒偨24bit偺 抣傪Ai傊擖傟傞丅

2僷乕僙儖柦椷021偼丄jkm僼傿乕儖僪偺22bit 偲嵟忋埵2bit偺0偱偱偒偨24bit 偺曗悢傪Ai傊擖傟傞丅曗悢偼丄偡傋偰偺1偺價僢僩傪0偵偟丄偡傋偰偺0偺價僢 僩傪1偵偡傞偙偲偱嶌傜傟傞丅柦椷021偼丄Ai偺嵟忋埵2bit傪1偵僙僢僩偡傞丅 偙偺柦椷偼丄晧偺抣傪Ai偵擖傟傞婡擻傪採嫙偡傞丅

偟偐偟丄偙偺柦椷偑晧偺悢傪擖傟傞偺偵巊梡偝傟傞側傜偽丄jkm僼傿乕儖僪偵 巊梡偡傞惓偺悢偼嵟廔揑偵婜懸偡傞晧偺悢偺愨懳抣偐傜1尭彮偝偣偰偍偐偹偽 側傜側偄丅(***栿拲: 僀儞僶乕僩屻偵2偺曗悢偵偡傞偨傔偵丄jkm偵擖傟傞悢偼丄 1尭偠偰偍偔***)

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷022 | ||||||

|---|---|---|---|---|---|---|

|

柦椷022偼丄jk僼傿乕儖僪偺6bit傪Ai偺壓埵6bit偵擖傟傞丅Ai偺嵟忋埵18bit偼 0偱偁傞丅晞崋奼挘偼柍偄丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

| 柦椷023 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

|

柦椷023ij0偼丄(Sj)偺壓埵24bit傪Ai傊擖傟傞丅(Sj)偺忋埵價僢僩偼柍帇偝傟 傞丅

柦椷023i01偼VL偺撪梕傪Ai傊擖傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

VL A1

A2 VL

偼丄 (A2)=100(敧恑) 偲側傞丅

VL A1

A2 VL

偼丄 (A2)=23(敧恑) 偲側傞丅

VL A1

A2 VL

偼丄 (A2)=23(敧恑) 偲側傞丅

| 柦椷024-025 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

|

柦椷024偼Bjk偺撪梕傪Ai傊擖傟傞丅

柦椷025偼Ai偺撪梕傪Bjk傊擖傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷026 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷026ij0偼(Sj)拞偺1偵僙僢僩偝傟偰偄傞價僢僩偺悢傪悢偊傞丄偦偟偰寢壥 傪Ai偺壓埵7bit偵擖傟傞丅Ai偺忋埵17bit偼0偱偁傞丅傕偟(Sj)=0側傜丄(Ai)=0 偱偁傞丅

柦椷026ij1偼(Sj)拞偺1偵僙僢僩偝傟偰偄傞價僢僩偺悢傪悢偊傞丅偦偟偰丄嵟 壓埵價僢僩偼寢壥偑婏悢偐嬼悢偐傪昞偟偰偍傝丄偦傟偑Aj偺嵟壓埵價僢僩埵抲 偵憲傜傟傞丅忋埵23bit偼僋儕傾偝傟傞丅億僺儏儗乕僔儑儞僇僂儞僩偦偺傕偺 偼揮憲偝傟側偄丅

柦椷026ij0偲026ij1偼億僺儏儗乕僔儑儞/儕乕僨傿儞僌丒僛儘丒僇僂儞僩婡擻 儐僯僢僩偱幚峴偝傟傞丅

柦椷026ij7偼丄CPU娫偱嫟桳偝傟偰偄傞SBj儗僕僗僞偺撪梕傪Aj傊憲傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷027 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

|

柦椷027ij0偼Sj偺儕乕僨傿儞僌丒僛儘偺悢傪悢偊丄寢壥傪Ai偺壓埵7bit偵擖傟

傞丅忋埵17bit偼0偱偁傞丅柦椷027ij0偼億僺儏儗乕僔儑儞/儕乕僨傿儞僌丒僛

儘丒僇僂儞僩婡擻儐僯僢僩偱幚峴偝傟傞丅

(栿拲: 儕乕僨傿儞僌丒僛儘偲偼丄1偺棫偭偰偄傞價僢僩傑偱偺忋埵價僢僩偺0

偺晹暘偱偁傞)

柦椷027ij7偼(Aj)傪丄摨堦僋儔僗僞拞偺CPU娫偱嫟桳偝傟偰偄傞SBj儗僕僗僞傊 奿擺偡傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷030-031 | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷030偼(Aj)偲(Ak)傪壛嶼偟偰丄寢壥傪Ai偵擖傟傞丅僆乕僶乕僼儘乕偼専弌 偝傟側偄丅

柦椷031偼(Aj)偲(Ak)傪尭嶼偟偰丄寢壥傪Ai偵擖傟傞丅僆乕僶乕僼儘乕偼専弌 偝傟側偄丅

柦椷030偲031偼傾僪儗僗壛嶼婡擻儐僯僢僩偱幚峴偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷032 | ||||||

|---|---|---|---|---|---|---|

|

柦椷032偼(Aj)偲(Ak)偺惍悢愊傪偲傝丄寢壥偺壓埵24bit傪Ai偵擖傟傞丅僆乕僶乕 僼儘乕偼専弌偝傟側偄丅

柦椷032偼丄傾僪儗僗忔嶼婡擻儐僯僢僩偱幚峴偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷033 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷033偼丄僠儍儞僱儖偺忬懺忣曬傪Ai偵擖傟傞丅j,k巜掕巕偲Aj偺撪梕偼丄梸 偟偰偄傞忣曬傪掕媊偡傞丅

j巜掕巕偑0偺帪丄妱傝崬傒梫媮偺嵟崅桪愭搙偺僠儍儞僱儖斣崋偑Ai傊擖傞丅Aj 偺撪梕偼j偑0偱側偄偲偒丄僠儍儞僱儖斣崋傪巜掕偡傞丅僠儍儞僱儖偺尰嵼傾僪 儗僗(Current Address:CA)儗僕僗僞偺抣偼丄k巜掕巕偑0偺帪丄Ai偵擖傞丅

僠儍儞僱儖偺僄儔乕僼儔僌偺抣偼丄k巜掕巕偑1偺帪丄Ai偺嵟壓埵價僢僩偵擖傞丅 Ai偺忋埵價僢僩偼僋儕傾偝傟傞丅僄儔乕僼儔僌偼丄儌僯僞丒儌乕僪偱柦椷0012 傪巊梡偟偰偺傒僋儕傾偱偒傞丅

柦椷033偼丄僠儍儞僱儖憖嶌偲姳徛偣偢丄儐乕僓偺幚峴傪朩偘側偄丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷034-037 | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷034偐傜037偼丄儊儌儕偲B,T儗僕僗僞娫偺僽儘僢僋揮憲傪峴偆丅

慡柦椷偵偍偄偰丄揮憲偝傟傞僨乕僞偺憤悢偼丄(Ai)偺壓埵7bit偱巜掕偝傟傞丅 惛偼丄摿庩忦審傪嶲徠丅

揮憲偵巊梡偝傟傞儗僕僗僞偺嵟弶偼丄jk偱巜掕偝傟傞丅揮憲偑恑峴偡傞偵偮傟丄 B.T儗僕僗僞偼B77偐T77偵側傞傑偱恑傓丅儗僕僗僞偺張棟偼丄娐忬偵峴傢傟傞丄 傛偭偰丄(Ai)偺僇僂儞僩偑廔傢偭偰偄側偗傟偽丄B77偺屻偼B00丄T77偺屻偼T00 偑張棟偝傟傞丅

揮憲柦椷偵傛偭偰嶲徠偝傟傞嵟弶偺儊儌儕斣抧偼丄(A0)偵傛偭偰巜掕偝傟傞丅 A0儗僕僗僞偺撪梕偼丄柦椷偺幚峴偵傛偭偰曄峏偝傟側偄丅儊儌儕嶲徠偼揮憲偺 恑峴偲偲傕偵1偯偮憹壛偡傞丅

B儗僕僗僞偺儊儌儕傊偺揮憲偼丄奺乆儚乕僪拞偺24bit塃媗偝傟丄忋埵40bit偼0 偵偝傟傞丅儊儌儕偐傜B儗僕僗僞傊偺揮憲偺帪丄壓埵24bit偑揮憲偝傟丄忋埵 40bit偼柍帇偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷040-041 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

|

2僷乕僙儖柦椷040偲041偼丄懄抣傪S傊擖傟傞丅

柦椷040偼丄22bit偺jkm僼傿乕儖僪偲忋埵42bit偺0偐傜側傞64bit偺抣傪Si偵擖 傟傞丅

柦椷041偼丄22bit偺jkm僼傿乕儖僪偲忋埵42bit偺0偐傜側傞抣偺僐儞僾儕儊儞 僩偺64bit偺抣傪Si偵擖傟傞丅僐儞僾儕儊儞僩偼丄偡傋偰偺1偺價僢僩傪0偵丄 偡傋偰偺0偺價僢僩傪1偵曄偊傞偙偲偱偱偒傞丅偟偨偑偭偰丄柦椷041偵傛傞丄 Si偺忋埵42bit 偼1偵僙僢僩偝傟傞丅偙偺柦椷偼丄Si偵晧偺抣傪擖傟傞偨傔偵 採嫙偝傟偰偄傞丅儗僕僗僞偺抣偼丄jkm偺1偺曗悢(僐儞僾儕儊儞僩)偱偁傞偐傜丄 2偺曗悢傪摼傞偨傔偵偼丄jkm偵偼丄-1偑梸偟偗傟偽0傪丄-2偑梸偟偗傟偽1傪丄- 4偑梸偟偗傟偽3丄側偳偲偟側偗傟偽側傜側偄丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷042-043 | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷042偼丄Si拞偵丄塃偐傜嵍偵64-jk屄偺1偑擖偭偨儅僗僋傪惗惉偡傞丅椺偊 偽丄jk=0側傜丄Si偼慡晹1偵側偭偨價僢僩(惍悢抣偺-1)傪帩偪丄jk=77(敧恑)側 傜丄Si偼嵟壓埵價僢僩埲奜偑慡晹0偵側偭偨價僢僩(惍悢抣偺1)傪帩偮丅

柦椷043偼丄Si拞偵丄嵍偐傜塃偵jk屄偺1偑擖偭偨儅僗僋傪惗惉偡傞丅椺偊偽丄 jk=0側傜丄Si偼慡晹0偵側偭偨價僢僩(惍悢抣偺0)傪帩偪丄jk=77(敧恑)側傜丄 Si偼嵟壓埵價僢僩埲奜偑慡晹1偵側偭偨價僢僩(惍悢抣偺-2)傪帩偮丅

柦椷042偲043偼僗僇儔榑棟婡擻儐僯僢僩偱幚峴偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷044-051 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

-------

拲堄

柦椷044偐傜051偱偼丄儗僕僗僞巜掕巕柍偟偺SB偼丄晞崋價僢僩偱偁傞丅嫟桳

傾僪儗僗丒儗僕僗僞偱偼側偔丅

-------

柦椷044偐傜051偼丄僗僇儔榑棟婡擻儐僯僢僩偱幚峴偝傟傞丅

柦椷044偼(Sj)偲(Sk)偺榑棟愊(AND)傪庢傝丄寢壥傪Si偵擖傟傞丅(Sj)偲(Sk)偺 懳墳偡傞價僢僩偑偲傕偵1偺帪丄Si偺價僢僩偑1 偵僙僢僩偝傟傞丅師偺椺偺傛 偆偵:

(Sj)= 1100

(Sk)= 1010

------

(Si)= 1000

傕偟丄j,k巜掕巕偑0偱側偄摨偠抣偺帪丄(Sj)偑Si偵揮憲偝傟傞丅傕偟丄j巜掕 巕偑0側傜丄Si偼僋儕傾偝傟傞丅傕偟丄j巜掕巕偑0偱側偔丄k巜掕巕偑0側傜丄 (Sj)偺晞崋價僢僩偑Si偵揮憲偝傟傞丅

柦椷045偼丄(Sk)偺僐儞僾儕儊儞僩偲(Sj)偺榑棟愊(AND)傪庢傝丄寢壥傪Si偵擖

傟傞丅(Sk)偺僐儞僾儕儊儞僩偲(Sj)偺懳墳偡傞價僢僩偲傕偵1偺帪丄Si偺價僢

僩偑1 偵僙僢僩偝傟傞丅師偺椺偺傛偆偵丅偙偙偱(Sk')偼(Sk)偺僐儞僾儕儊儞

僩偱偁傞:

傕偟 (Sk)=1010側傜

(Sj) = 1100

(Sk')= 0101

------

(Si) = 0100

傕偟丄j,k巜掕巕偑摨偠抣偐丄j巜掕巕偑0側傜丄Si偼僋儕傾偝傟傞丅傕偟丄j巜 掕巕偑0偱側偔丄k巜掕巕偑0側傜丄(Sj)偺晞崋價僢僩偑僋儕傾偝傟偰Si偵揮憲 偝傟傞丅

柦椷046偼(Sj)偲(Sk)偺榑棟嵎(攔懠揑榑棟榓;EOR)傪庢傝丄寢壥傪Si偵擖傟傞丅 (Sj)偲(Sk)偺懳墳偡傞價僢僩偑堘偆偲偒丄Si偺價僢僩偑1 偵僙僢僩偝傟傞丅師 偺椺偺傛偆偵:

(Sj)= 1100

(Sk)= 1010

------

(Si)= 0110

傕偟丄j,k巜掕巕偑0偱側偄摨偠抣偺帪丄Si偼僋儕傾偝傟傞丅傕偟丄j巜掕巕偑0 偱丄k巜掕巕偑0偱側偄側傜丄(Sk)偑Si偵揮憲偝傟傞丅傕偟丄j巜掕巕偑0偱側偔丄 k巜掕巕偑0側傜丄(Sj)偺晞崋價僢僩偑斀揮偝傟丄Si偵揮憲偝傟傞丅

柦椷047偼(Sj)偲(Sk)偺榑棟揑堦抳(栿拲:EOR偺斀揮)傪庢傝丄寢壥傪Si偵擖傟 傞丅(Sj)偲(Sk)偺懳墳偡傞價僢僩偑摨偠偲偒丄Si偺價僢僩偑1 偵僙僢僩偝傟傞丅 師偺椺偺傛偆偵:

(Sj)= 1100

(Sk)= 1010

------

(Si)= 1001

傕偟丄j,k巜掕巕偑0偱側偄摨偠抣偺帪丄Si偼偡傋偰1偑僙僢僩偝傟傞丅傕偟丄j 巜掕巕偑0偱丄k巜掕巕偑0偱側偄側傜丄(Sk)偺僐儞僾儕儊儞僩偑Si偵揮憲偝傟 傞丅傕偟丄j巜掕巕偑0偱側偔丄k巜掕巕偑0側傜丄(Sj)偺晞崋價僢僩傪彍偔偡傋 偰偺價僢僩偑斀揮偝傟丄寢壥偑Si偵揮憲偝傟傞丅寢壥偼丄柦椷046偵傛偭偰惗 惉偝傟偨傕偺偺斀揮偱偁傞丅

柦椷050偼(Sk)拞偺1偺儅僗僋偵傛偭偰丄(Sj)偲(Si)偺撪梕傪儅乕僕偡傞丅寢壥

偼丄師偺榑棟曽掱幃偱掕媊偝傟傞丅偙偙偱Sk'偼Sk偺僐儞僾儕儊儞僩(斀揮) 偱

偁傞:

(Si)= (Sj)(Sk) + (Si)(Sk')

傕偟丄(Sk)=11110000側傜

(Sk')=00001111

(Si) =11001100

(Sj) =10101010

-----------

(Si) =10101100

柦椷050偼丄64bit儚乕僪偺堦晹傪儅乕僕偟偰丄慻傒崌傢偣偨儚乕僪偵偡傞偙偲 傪堄恾偟偰偄傞丅傕偟丄j巜掕巕偑0偱丄k巜掕巕偑0偱側偄側傜丄Sk偺懳墳偡傞 價僢僩偑1偺帪丄Si偺價僢僩偼僋儕傾偝傟傞丅傕偟丄j巜掕巕偑0偱側偔丄k巜掕 巕偑0側傜丄(Sj)偺晞崋價僢僩偼Si偺晞崋價僢僩偵抲偒姺傢傞丅傕偟丄j,k巜掕 巕偑椉曽0偺帪丄Si偺晞崋價僢僩偼僋儕傾偝傟傞丅

柦椷051偼丄(Sj)偲(Sk)偺榑棟榓(OR)傪庢傝丄寢壥傪So偵擖傟傞丅(Sj)偲(Sk) 偺懳墳偡傞價僢僩偺偳偪傜偐偑1偺帪丄Si偺價僢僩偑僙僢僩偝傟傞丅師偺椺偺 傛偆偵:

(Sj)= 1100

(Sk)= 1010

-----

(Si)= 1110

傕偟丄j,k巜掕巕偑0偱側偄摨偠抣偺帪丄Si偵(Si)偑揮憲偝傟傞丅傕偟丄j巜掕 巕偑0偱丄k巜掕巕偑0偱側偄側傜丄(Sk) 偑Si偵揮憲偝傟傞丅傕偟丄j巜掕巕偑0 偱側偔丄k巜掕巕偑0側傜丄(Sj)偺晞崋價僢僩傪1偵偟偰丄Si偵揮憲偝傟傞丅傕 偟丄j,k巜掕巕偑椉曽0偺帪丄Si偺晞崋價僢僩偺傒偐傜側傞1偺儅僗僋偑Si偵擖 傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 052 - 055 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷052偐傜055偼僗僇儔丒僔僼僩婡擻儐僯僢僩偱幚峴偝傟傞丅S儗僕僗僞拞偺 抣傪jk偱巜掕偝傟偨暘偩偗僔僼僩偡傞丅偳偺僔僼僩傕廔抂偐傜偼0偑枮偨偝傟 傞丅

柦椷052偼(Si)傪jk偩偗嵍偵僔僼僩偟丄寢壥傪S0偵擖傟傞丅僔僼僩暆偼0偐傜63 嵍偱偁傞丅

柦椷053偼(Si)傪64-jk偩偗塃偵僔僼僩偟丄寢壥傪S0偵擖傟傞丅僔僼僩暆偼1偐 傜64塃偱偁傞丅

柦椷054偼(Si)傪jk偩偗嵍偵僔僼僩偟丄寢壥傪Si偵擖傟傞丅僔僼僩暆偼0偐傜63 嵍偱偁傞丅

柦椷055偼(Si)傪64-jk偩偗塃偵僔僼僩偟丄寢壥傪Si偵擖傟傞丅僔僼僩暆偼1偐 傜64塃偱偁傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 056 - 057 | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷056偐傜057偼僗僇儔丒僔僼僩婡擻儐僯僢僩偱幚峴偝傟傞丅

榑棟揑偵偮側偑傟偨S儗僕僗僞偺128bit偺抣傪僔僼僩偡傞丅僔僼僩悢偼Ak儗僕 僗僞偵曐帩偝傟傞丅偡傋偰偺僔僼僩悢(Ak)偼丄惓偱偁傞偲峫偊傜傟丄(Ak)偺 24bit偡傋偰偑僔僼僩悢偵巊梡偝傟傞丅傕偟k巜掕巕偑0側傜丄1價僢僩僔僼僩偲 側傞丅傕偟j=0側傜丄僔僼僩偝傟傞悢偼丄Sj偺抣偵偼0偑巊梡偝傟傞偺偱丄 128bit偲偄偆傛傝丄64bit偱偁傞丅

僔僼僩悢偑64傪挻偊偢丄i偲j巜掕巕偑摨偠偱偐偮0偱側偗傟偽丄僔僼僩偼娐忬 偱偁傞丅柦椷056偲057偱偼丄i亗j偱梌偊傜傟偨傜丄(Sj)偼曄壔偟側偄丅僔僼僩 悢偑64傛傝戝偒偗傟偽廔抂偐傜0偑枮偨偝傟傞丅傕偟i=j偱僔僼僩悢偑64傛傝戝 偒偗傟偽丄偦傟偧傟柦椷054偐055傪僔僼僩悢64 傛傝彫偝偄悢偱巊偭偨帪偲摨 偠僔僼僩偱偁傞丅

柦椷056偼丄嵟弶偵丄(Si)偑2偮偺儗僕僗僞偺嵟忋埵價僢僩傪帩偭偰偄傞偲偟偰丄 (Si)偲(Sj)偺嵍僔僼僩傪峴偆丅寢壥偺忋埵64bit偑Si偵憲傜傟傞丅僔僼僩悢偑 127傪挻偊傞帪丄Si偼僋儕傾偝傟傞丅柦椷056偼丄僔僼僩悢偑63傪挻偊偢丄j巜 掕巕偑0偺偲偒丄柦椷054偲摨偠寢壥傪惗惉偡傞丅

柦椷057偼嵟弶偵丄(Sj)偑2偮偺儗僕僗僞偺嵟忋埵價僢僩傪帩偭偰偄傞偲偟偰丄 (Sj)偲(Si)偺塃僔僼僩傪峴偆丅寢壥偺壓埵64bit偑Si偵憲傜傟傞丅僔僼僩悢偑 127傪挻偊傞帪丄Si偼僋儕傾偝傟傞丅柦椷057偼丄僔僼僩悢偑63傪挻偊偢丄j巜 掕巕偑0偺偲偒丄柦椷055偲摨偠寢壥傪惗惉偡傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 060 - 061 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷060偼(Sj)偲(Sk)偺惍悢榓傪偲傝丄寢壥傪Si偵擖傟傞丅僆乕僶乕僼儘乕偼 専弌偝傟側偄丅

柦椷061偼(Sj)偲(Sk)偺惍悢嵎傪偲傝丄寢壥傪Si偵擖傟傞丅僆乕僶乕僼儘乕偼 専弌偝傟側偄丅

柦椷060偲061偼僗僇儔壛嶼婡擻儐僯僢僩偱幚峴偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 062 - 063 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷062偲063偼丄晜摦彫悢揰壛嶼儐僯僢僩偱幚峴偝傟傞丅僆儁儔儞僪偼晜摦彫 悢揰宍幃偱偁傞偲憐掕偝傟傞丅僆儁儔儞僪偑惓婯壔偝傟偰偄側偔偰傕丄寢壥偼 惓婯壔偝傟傞丅

柦椷062偼Sj偲Sk偺晜摦彫悢揰検偺榓傪庢偭偰丄惓婯壔偝傟偨寢壥傪Si偵擖傟 傞丅

柦椷063偼Sj偲Sk偺晜摦彫悢揰検偺嵎傪庢偭偰丄惓婯壔偝傟偨寢壥傪Si偵擖傟 傞丅

僆乕僶乕僼儘乕忦審偵偮偄偰偼4復偵婰弎偝傟偰偄傞丅晞崋價僢僩偺僙僢僩

(bit=1)偝傟偨晜摦彫悢揰僆儁儔儞僪偱偼丄巜悢0偱壖悢0側傜0(64bit慡晹0)偲

偟偰埖傢傟傞(拲++)丅

(拲++: -0偲峫偊傞丅晜摦彫悢揰忔嶼婡擻儐僯僢僩偵偍偄偰曅曽偺僆儁儔儞僪

偑-0偱偁傞応崌傪彍偄偰丄晜摦彫悢揰儐僯僢僩偑-0傪惗惉偡傞偙偲偼側偄丅捠

忢丄悢偵晞崋傪晅偗傛偆偲偡傞榑棟憖嶌偱-0偑敪惗偡傞;偦傟偼0偱偁傠偆丅)

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 064 - 067 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷064偐傜067偼晜摦彫悢揰忔嶼儐僯僢僩偱幚峴偝傟傞丅僆儁儔儞僪偼晜摦彫 悢揰宍幃偱偁傞偲憐掕偝傟傞丅僆儁儔儞僪偑惓婯壔偝傟偰偄側偄帪丄寢壥偑惓 婯壔偝傟偰偄傞偙偲偼曐徹偝傟側偄丅

柦椷064偼Sj偲Sk偺晜摦彫悢揰検偺愊傪庢偭偰丄寢壥傪Si偵擖傟傞丅

柦椷065偼Sj偲Sk偺晜摦彫悢揰検偺敿惛搙偺娵傔傜傟偨愊傪庢偭偰丄寢壥傪Si 偵擖傟傞丅寢壥偺壓埵19bit偼僋儕傾偝傟傞丅

柦椷066偼Sj偲Sk偺晜摦彫悢揰検偺娵傔傜傟偨愊傪庢偭偰丄寢壥傪Si偵擖傟傞丅

柦椷067偼Sj偲Sk偺晜摦彫悢揰検偺愊傪庢傝丄偦傟傪2偐傜堷偄偨寢壥傪Si偵擖 傟傞丅偙偺柦椷偼丄4復晜摦彫悢揰嶼弍墘嶼偱愢柧偝傟偨丄彍嶼僔乕働儞僗偱 巊梡偝傟傞丅

C=2-B*A偺昡壙偵偍偄偰丄B偼忋埵47價僢僩傛傝彫偝偄A偺偦偺媡悢偱偁傝丄惓 妋側媡悢偱偼側偄丅偦偆偱側偗傟偽丄C偼晄惓妋偱偁傠偆丅媡悢嬤帡柦椷偵傛偭 偰惗惉偝傟傞媡悢偼丄偙偺婯斖偵崌抳偟偰偄傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 070 | ||||||

|---|---|---|---|---|---|---|

|

柦椷070偼媡悢嬤帡婡擻儐僯僢僩偱幚峴偝傟傞丅

柦椷070偼丄Sj撪偺惓婯壔偝傟偨晜摦彫悢揰検偺媡悢偺嬤帡偺寢壥傪Si偵擖傟 傞丅偙偺柦椷偼丄4復偺晜摦彫悢揰嶼弍墘嶼偱弎傋傜傟偰偄傞2偮偺晜摦彫悢揰 悢検偺彍嶼僔乕働儞僗偵尰傟傞丅

媡悢嬤帡柦椷偼寢壥傪忋埵30bit偵惗惉偡傞丅壓埵18bit偼0偱偁傞丅忋埵價僢 僩偼媡悢孞傝曉偟柦椷偲忔嶼傪巊梡偟偰丄48bit偵奼挘偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 071 | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷071偼j巜掕巕偺抣偵埶懚偟偰婡擻傪幚峴偡傞丅A儗僕僗僞偐傜S儗僕僗僞傊 偺忣曬偺揮憲偲丄昿斏偵巊梡偡傞晜摦彫悢揰掕悢偺惗惉偑偦偺婡擻偱偁傞丅

j巜掕巕偑0側傜丄Ak拞偺24bit偺抣傪Si傊揮憲偡傞丅抣偼晞崋柍偟惍悢偲偟偰 埖傢傟傞丅Si偺忋埵價僢僩偼0偲側傞丅

j巜掕巕偑1側傜丄Ak拞偺24bit偺抣傪Si傊揮憲偡傞丅抣偼晞崋晅偒惍悢偲偟偰 埖傢傟傞丅Ak偺晞崋價僢僩偑Si偺忋埵價僢僩偵奼挘偝傟傞丅

j巜掕巕偑2側傜丄Ak拞偺24bit偺抣傪旕惓婯壔晜摦彫悢揰悢偲偟偰Si傊揮憲偡 傞丅(寢壥傪惓婯壔偡傞偵偼丄0偲偺壛嶼傪峴偆) 偙偺柦椷偱偼丄價僢僩2^62偐 傜2^48傑偱偵懚嵼偡傞巜悢晹偑40060(敧恑)偵僙僢僩偝傟傞丅壖悢晹偺晞崋偼 Ak偺晞崋偵廬偭偰僙僢僩偝傟傞丅Ak偺晞崋價僢僩偑僙僢僩偝傟偰偄傟偽丄Ak偺 2偺曗悢偑壖悢晹偺戝偒偝偲偟偰Si偵擖傟傜傟丄偦偟偰丄Si偺價僢僩2^63偼壖 悢晹偺晞崋偲偟偰僙僢僩偝傟傞丅(栿拲: 壖悢晹偼晞崋價僢僩傪彍偔偲丄愨懳 抣(惓悢)偱曐帩偡傞丅壖悢晹偺晞崋偼丄價僢僩2^63偵抲偔)

偦偺愨懳抣偑24bit傛傝彫偝偄惍悢傪晜摦彫悢揰悢偵曄姺偡傞柦椷偺僔乕働儞 僗:

CAL code: A1 S1

S1 +FA1

S1 +FS1 9CP昁梫

j巜掕巕偑3側傜丄掕悢0.75亊2^48 偑Si偵擖傟傜傟傞丅(0 40060 6000 0000 0000 0000(敧恑)) 偙偺掕悢偼丄愨懳抣偑47價僢僩傛傝彫偝側惍悢(惓悢偱傕晧 悢偱傕) 偐傜丄晜摦彫悢揰悢傪惗惉偡傞偺偵巊梡偝傟傞丅

Si拞偺惍悢傪曄姺偡傞柦椷楍:

CAL code: S2 0.6

S1 S2-S1

S1 S2-FS1 11CP昁梫

j巜掕巕偑4側傜丄掕悢0.5 (= 0 40000 4000 0000 0000 0000(敧恑)) 偑Si偵擖 傟傜傟傞丅

j巜掕巕偑5側傜丄掕悢1.0 (= 0 40001 4000 0000 0000 0000(敧恑)) 偑Si偵擖 傟傜傟傞丅

j巜掕巕偑6側傜丄掕悢2.0 (= 0 40002 4000 0000 0000 0000(敧恑)) 偑Si偵擖 傟傜傟傞丅

j巜掕巕偑7側傜丄掕悢4.0 (= 0 40003 4000 0000 0000 0000(敧恑)) 偑Si偵擖 傟傜傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 072 - 075 | |||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||

| (拲+: 尰嵼偼枹僒億乕僩) |

柦椷072i00偼丄儕傾儖僞僀儉丒僋儘僢僋(RTC)偺64bit偺抣傪Si偵擖傟傞丅僋儘僢 僋偼丄枅CP偛偲偵1僀儞僋儕儊儞僩偝傟傞丅RTC偼丄儌僯僞偺傒偵傛偭偰丄柦椷 0014j0偺巊梡傪捠偟偰僙僢僩偱偒傞丅

柦椷072i02偼丄慡僙儅僼僅偺抣傪Si偵擖傟傞丅32bit偺SM儗僕僗僞偼丄SM00偑 晞崋價僢僩偵側傞傛偆偵丄Si偵嵍媗偝傟傞丅

柦椷072i03偼丄STj偺撪梕傪丂Si偵擖傟傞丅

柦椷073i00偼丄VM儗僕僗僞偺64bit偺抣傪Si偵擖傟傞丅VM儗僕僗僞偼丄捠忢丄 柦椷175偱僙僢僩偝傟偨屻偵撉傑傟傞丅

柦椷073i11偼惈擻娔帇偵巊梡偝傟丄儌僯僞丒儌乕僪偺摿尃偱偁傞丅073i11柦椷 偺奺幚峴偼億僀儞僞傪恑傔丄偦偟偰惈擻僇僂儞僞偺忋埵價僢僩偐壓埵價僢僩偐 傪Si偺忋埵價僢僩偵擖傟傞丅惈擻僇僂儞僞偺忣曬偼晅榐C傪嶲徠偺偙偲丅

柦椷073i21偲073i31偼丄SECDEC儊儞僥僫儞僗丒儌乕僪婡擻偺堦晹偱丄儊僀儞 僼儗乕儉偺惂屼僷僱儖偺儊僀儞僥僫儞僗丒儌乕僪丒僗僀僢僠偑ON偺帪偩偗偟偐 幚峴偝傟側偄丅073i21偼丄堷偒懕偔儊儌儕彂偒崬傒(I/O偺儊儌儕彂偒崬傒偼彍 偔)偱彂偒崬傑傟傞丄SECDED偱巊梡偝傟傞8僠僃僢僋丒價僢僩傪丄偁傞僨乕僞丒 價僢僩偱抲偒姺偊傞偙偲傪壜擻偵偡傞丅柦椷073i31偼丄3偮偺SECDED儊儞僥僫 儞僗丒儌乕僪柦椷001501, 001521, 001531偺偡傋偰傪僋儕傾偡傞丅SECDEC儊儞 僥僫儞僗丒儌乕僪偺姰慡側忣曬偵偮偄偰偼晅榐D傪嶲徠丅

柦椷073ij1偼忬懺儗僕僗僞SRj偺撪梕傪丄Si偵擖傟傞丅柦椷073i01偼Si偺忋埵 價僢僩偵師偺忬懺傪曉偡:

Si價僢僩 愢柧 2^63 僋儔僗僞壔嵪傒, CLN # 0 (CL) 2^57 僾儘僌儔儉丒僗僥乕僞僗 (PS) 2^51 晜摦彫悢揰僄儔乕敪惗 (FPS) 2^50 晜摦彫悢揰妱崬傒嫋壜 (IFP) 2^49 僆儁儔儞僪斖埻妱崬傒嫋壜(IOR) 2^48 憃曽岦儊儌儕嫋壜 (BDM) 2^40(拲+) 僾儘僙僢僒斣崋價僢僩0 (PN0) 2^33(拲+) 僋儔僗僞斣崋價僢僩1 (CLN1) 2^32(拲+) 僋儔僗僞斣崋價僢僩0 (CLN0) (拲+: 儌僯僞丒儌乕僪偱偺幚峴偱側偗傟偽丄偙傟傜偺價僢僩偺埵抲偼抣0傪曉偡)

柦椷073i02偼Si偺忋埵32bit偵忋偐傜丄僙儅僼僅傪僙僢僩偡傞SM00偼Si偺晞崋 價僢僩偵庴偗庢傜傟傞丅

柦椷073ij3偼丄Si偺撪梕傪STj偵擖傟傞丅

柦椷074偼丄Tjk偺撪梕傪Si偵擖傟傞丅

柦椷075偼丄Si偺撪梕傪Tjk偵擖傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 076 - 077 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷076偲077偼丄64bit偺検傪V儗僕僗僞梫慺偲S儗僕僗僞偺娫偱揮憲偡傞丅

柦椷076偼丄Vj儗僕僗僞偺梫慺偺撪梕傪Sj偵揮憲偡傞丅

柦椷077偼丄Sj儗僕僗僞偺撪梕傪Vj儗僕僗僞偺梫慺偵揮憲偡傞丅

(Ak)偺壓埵6bit偼丄奺柦椷偺偨傔偺儀僋僩儖偺梫慺傪寛掕偡傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 10h - 13h | |||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

2僷乕僙儖柦椷10h偐傜13h偼丄儊儌儕偲A儗僕僗僞偐S儗僕僗僞偺娫偱僨乕僞傪 揮憲偡傞丅Ah偺撪梕(晞崋晅偺22bit惍悢偲偟偰埖傢傟傞) 偼丄jkm僼傿乕儖僪 偺晞崋晅22bit惍悢偲壛嶼偝傟偰丄儊儌儕偺傾僪儗僗傪寛掕偡傞丅傕偟h偑0側 傜丄(Ah)偼0偱偁傝丄jkm僼傿乕儖僪偩偗偑傾僪儗僗偵巊梡偝傟傞丅傾僪儗僗嶼 弍墘嶼偼丄傾僪儗僗壛嶼婡擻儐僯僢僩偲摨條偩偑丄偦傟偐傜暘棧偝傟偨傾僪儗 僗壛嶼婍偵傛偭偰幚峴偝傟傞丅

柦椷10h偲11h偼A儗僕僗僞偐傜,傑偨偼A傊24bit検傪揮憲偡傞丅儊儌儕偐傜A儗僕僗僞傊 僨乕僞傪揮憲偡傞偲偒偼丄儊儌儕丒儚乕僪偺忋埵40bit偼柍帇偝傟傞丅Ai偐傜 儊儌儕傊偺僗僩傾帪偼丄儊儌儕偺忋埵40bit偼0偱偁傞丅

柦椷12h偲13h偼Si儗僕僗僞偐傜,傑偨偼Si傊64bit検傪揮憲偡傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 140 - 147 | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

戞2儀僋僩儖榑棟婡擻儐僯僢僩晅偒偺儊僀儞僼儗乕儉偱偼丄柦椷140偐傜145偼丄 僼儖丒儀僋僩儖偐丄戞擇儀僋僩儖榑棟儐僯僢僩偑嫋壜偝傟偰採嫙偝傟偰偄傞側 傜戞擇儀僋僩儖榑棟儐僯僢僩偱幚峴偱偒傞丅傕偟丄戞擇儀僋僩儖榑棟儐僯僢僩 偑嬛巭偝傟偰偄傟偽丄柦椷140偐傜145偼丄僼儖丒儀僋僩儖榑棟儐僯僢僩偩偗偱 幚峴偱偒傞丅

柦椷146偲147偼丄僼儖丒儀僋僩儖榑棟儐僯僢僩偩偗偱幚峴偡傞丅幚峴偝傟傞憖 嶌偺悢偼丄VL儗僕僗僞偺撪梕偱寛掕偝傟傞丅偡傋偰偺憖嶌偼丄Vi,Vj,Vk儗僕僗 僞偺梫慺0偐傜巒傑傝丄奺憖嶌偑幚峴偝傟傞偛偲偵1偯偮梫慺斣崋偑憹壛偡傞丅 偡傋偰偺寢壥偼丄Vi偵攝憲偝傟傞丅

柦椷140,142,144,146偱偼丄Sj偺撪梕偺僐僺乕偑婡擻儐僯僢僩傊憲傜傟傞丅憖 嶌偺姰椆傑偱撪梕偺僐僺乕偼僆儁儔儞僪偺堦偮偲偟偰曐帩偝傟傞丅廬偭偰丄Sj 偼丄儀僋僩儖憖嶌偺塭嬁側偟偵懄嵗偵曄壔偝偣傜傟傞偙偲偑偱偒傞丅柦椷 141.143.145,147偱偼偡傋偰偺僆儁儔儞僪偼丄V儗僕僗僞偐傜摼傜傟傞丅

柦椷140偲141偼僆儁儔儞僪偺慻偺榑棟愊(AND) 傪嶌傝丄寢壥傪Vi偵擖傟傞丅 (Sj)偐(Vj偺梫慺)偲(Vk偺梫慺)偑1側傜偽丄Vi偺梫慺偺價僢僩偼1偵僙僢僩偝傟 傞丄師偺傛偆偵:

(Sj) 偐 (Vj偺梫慺) = 1100

(Vk偺梫慺) = 1010

---------

(Vi偺梫慺) = 1000

柦椷142偲143偼僆儁儔儞僪偺慻偺榑棟榓(OR) 傪嶌傝丄寢壥傪Vi偵擖傟傞丅 (Sj)偐(Vj偺梫慺)偲(Vk偺梫慺)偺偳傟偐偑1側傜偽丄Vi偺梫慺偺價僢僩偼1偵僙僢 僩偝傟傞丄師偺傛偆偵:

(Sj) 偐 (Vj偺梫慺) = 1100

(Vk偺梫慺) = 1010

---------

(Vi偺梫慺) = 1110

柦椷144偲145偼僆儁儔儞僪偺慻偺榑棟嵎(EOR) 傪嶌傝丄寢壥傪Vi偵擖傟傞丅 (Sj)偐(Vj偺梫慺)偲(Vk偺梫慺)偐傜偺嵎偑Vi偺梫慺偺價僢僩偵僙僢僩偝傟傞丄 師偺傛偆偵:

(Sj) 偐 (Vj偺梫慺) = 1100

(Vk偺梫慺) = 1010

---------

(Vi偺梫慺) = 0110

柦椷146偲147偼丄VM儗僕僗僞偺撪梕偵埶懚偟偰丄僆儁儔儞僪傪Vi偵揮憲偡傞丅 儅僗僋偺價僢僩2^63偼V儗僕僗僞偺梫慺0偵懳墳偟偰偄傞丅價僢僩2^0偼V儗僕僗 僞偺梫慺63偵懳墳偟偰偄傞丅慖戰偵巊梡偝傟傞僆儁儔儞僪偺慻偼丄柦椷偵埶懚 偟偰偄傞丅柦椷146偱偼丄戞1僆儁儔儞僪偼忢偵(Sj)偱丄戞2僆儁儔儞僪偼(Vk偺 梫慺)偱偁傞丅柦椷147偱偼丄戞1僆儁儔儞僪偼(Vj偺梫慺)偱戞2僆儁儔儞僪偼 (Vk偺梫慺)偱偁傞丅傕偟儀僋僩儖丒儅僗僋偺價僢僩n偑1側傜丄戞1僆儁儔儞僪 偑揮憲偝傟傞; 傕偟儀僋僩儖丒儅僗僋偺價僢僩n偑0側傜丄戞2僆儁儔儞僪(Vk偺 梫慺)偑慖戰偝傟傞丅

椺:

1. 傕偟柦椷146偑幚峴偝傟傞偲偟偰丄 師偺儗僕僗僞忦審偑偁偭偨傜:

(VL) = 4 (VM) = 0 60000 0000 0000 0000 0000 (S2) = -1 (V600) = 1 (V601) = 2 (V602) = 3 (V603) = 4柦椷146726偑幚峴偝傟傞偲丅埲壓偺幚峴丄V7偺嵟弶偺4梫慺偑師偺抣偵側傞:

(V700) = 1 (V701) = -1 (V702) = -1 (V703) = 4V7偺巆傝偺梫慺偼曄壔偟側偄丅

2. 傕偟柦椷147偑幚峴偝傟傞偲偟偰丄師偺儗僕僗僞忦審偑偁偭偨傜:

(VL) = 4 (VM) = 0 60000 0000 0000 0000 0000 (S2) = -1 (V200) = 1 (V300) = -1 (V201) = 2 (V301) = -2 (V202) = 3 (V302) = -3 (V203) = 4 (V303) = -4柦椷147123偑幚峴偝傟傞偲丅埲壓偺幚峴丄V1偺嵟弶偺4梫慺偑師偺抣偵側傞:

(V100) = -1 (V101) = 2 (V102) = 3 (V103) = -4V1偺巆傝偺梫慺偼曄壔偟側偄丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

(拲+: 儀僋僩儖柦椷偼懄嵗偵幚峴奐巒偟偨傝丄偟側偐偭偨傝偡傞; 僨乕僞偑 棙梡壜擻偵側偭偨帪偵幚峴偡傞丅摿偵丄儀僋僩儖偺偄偔偮偐偺梫慺偺儘乕僪偺 幚峴傪抶偔偡傞儊儌儕嫞崌偼丄儘乕僪偐傜巒傑傞僆儁儗乕僔儑儞丒僠僃僀儞偺 偡傋偰偺柦椷偺抶墑傪堷偒婲偙偡偙偲偑偁傞丅)

(拲++: 戞擇儀僋僩儖榑棟婡擻儐僯僢僩晅偒偺儊僀儞僼儗乕儉偺応崌偩偗) pp 5-67 (p 181) ****************----------------***********

| 柦椷 150 -151 | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷150偲151偼儀僋僩儖丒僔僼僩婡擻儐僯僢僩偱幚峴偝傟傞丅幚峴偝傟傞憖嶌 偺悢偼VL儗僕僗僞偺撪梕偱寛掕偝傟傞丅憖嶌偼丄Vi偲Vj儗僕僗僞偺梫慺偺0偐 傜奐巒偟丄(VL)-1偱巜掕偝傟偨梫慺偱廔傢傞丅

慡偰偺僔僼僩偼丄廔抂傑偱0偱杽傔傜傟傞丅僔僼僩悢偼(Ak)偐傜摼傜傟丄Ak偺 24bit偡傋偰偑僔僼僩悢偲偟偰巊梡偝傟傞丅傕偟僔僼僩悢偑63傪挻偊偨傜丄Vi 偺梫慺偼僋儕傾偝傟傞丅偡傋偰偺僔僼僩悢(Ak)偼惓悢偲偟偰埖傢傟傞丅

僔僼僩柦椷052偐傜055偲堘偭偰丄偙傟傜偺柦椷偼jk僼傿乕儖僪偱偼側偔丄Ak偐 傜僔僼僩悢傪庴偗庢傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

(拲++: 儀僋僩儖柦椷偼懄嵗偵幚峴奐巒偟偨傝丄偟側偐偭偨傝偡傞; 僨乕僞偑 棙梡壜擻偵側偭偨帪偵幚峴偡傞丅摿偵丄儀僋僩儖偺偄偔偮偐偺梫慺偺儘乕僪偺 幚峴傪抶偔偡傞儊儌儕嫞崌偼丄儘乕僪偐傜巒傑傞僆儁儗乕僔儑儞丒僠僃僀儞偺 偡傋偰偺柦椷偺抶墑傪堷偒婲偙偡偙偲偑偁傞丅)

摿庩忦審:

| 柦椷 152 -153 | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷152偲153偼儀僋僩儖丒僔僼僩婡擻儐僯僢僩偱幚峴偝傟傞丅柦椷偼丄榑棟揑 偵偮側偑傟偨Vj儗僕僗僞偺2偮偺梫慺偺撪梕偱偁傞128bit偺抣傪僔僼僩偡傞丅 僔僼僩偺曽岦偑丄Vi偵憲傜傟傞寢壥偑丄忋埵價僢僩偐壓埵價僢僩偐傪寛掕偡傞丅 僔僼僩悢偼Ak儗僕僗僞偐傜摼傜傟傞丅

慡偰偺僔僼僩偺廔抂偼0偱杽傔傜傟傞丅

憖嶌偺悢偼丄VL儗僕僗僞偺撪梕偱寛傔傜傟傞丅

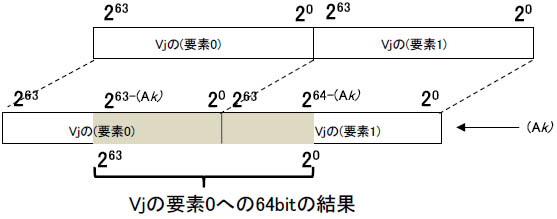

柦椷152偼嵍僔僼僩傪幚峴偡傞丅憖嶌偼丄Vj偺梫慺0偐傜奐巒偡傞丅傕偟(VL)偑 1側傜丄梫慺0偼64bit偺0偲堦弿偵偮側偑傟丄偦偟偰丄128bit検偲偟偰(Ak)偱巜 掕偝傟偨偩偗嵍偵僔僼僩偝傟寢壥偲側傞丅偨偩1偮偺憖嶌偩偗偑幚峴偝傟傞丅 巆偭偨忋埵64bit偑Vi偺梫慺0偵憲傜傟傞丅(栿拲: 64屄偺0偼丄壓埵64bit偵偮 側偑傟傞)

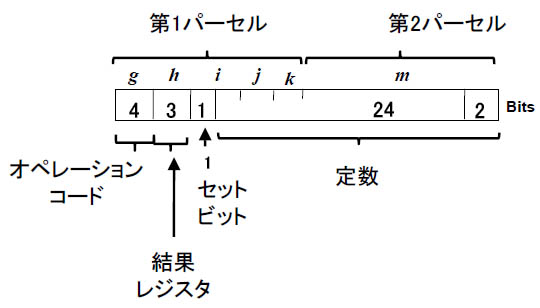

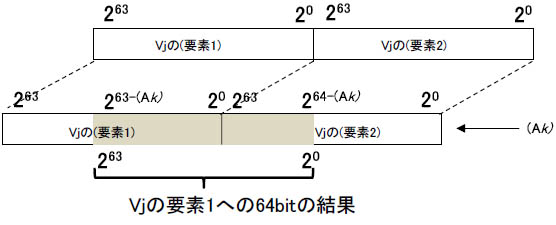

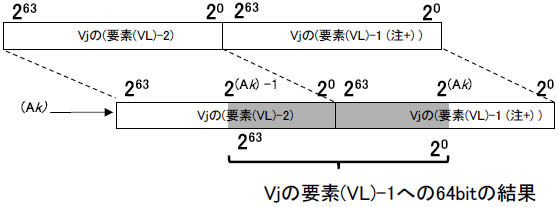

傕偟(VL)偑2側傜丄憖嶌偼梫慺0偐傜奐巒偝傟丄Vj偺梫慺0偼梫慺1偲堦弿偵偮側 偑傟丄偦偟偰丄128bit検偲偟偰(Ak)偱巜掕偝傟偨偩偗嵍偵僔僼僩偝傟寢壥偲側 傞丅巆偭偨忋埵64bit偑Vi偺梫慺0偵憲傜傟傞丅恾5-7偑偙偺憖嶌傪恾夝偡傞丅

傕偟(VL)偑2傛傝戝偒偄側傜丄梫慺1偲梫慺2傪偮側偄偱憖嶌偼宲懕偟丄64bit偺 寢壥傪Vi偺梫慺1偵憲傞丅恾5-8偑偙偺憖嶌傪恾夝偡傞丅

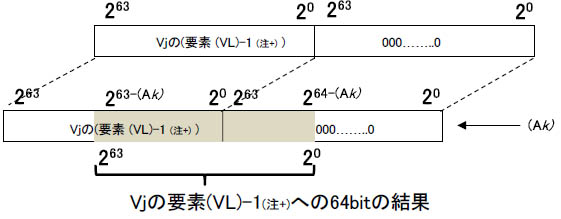

傕偟(VL)偑2側傜丄梫慺1偼64bit偺0偲堦弿偵偮側偑傟丄偦偟偰丄偨偩2偮偺憖 嶌偩偗偑幚峴偝傟傞丅堦斒揑偵丄(VL)偵傛偭偰寛傔傜傟偨Vj偺嵟屻偺梫慺偼 64bit偺0偲偮側偑傟傞丅恾5-9偑偙偺憖嶌傪恾夝偡傞丅 pp 5-70 --- pp 5-71

傕偟(Ak)偑128埲忋側傜丄寢壥偼偡傋偰0偲側傞丅傕偟(Ak)偑64傛傝戝偒偄側傜丄 寢壥儗僕僗僞偼丄彮側偔偲傕(Ak)-64屄偺0傪娷傓丅

椺:

1. 傕偟柦椷152偑幚峴偝傟傞偲偟偰丄師偺儗僕僗僞忦審偑偁偭偨傜:

(VL) = 4 (A1) = 3 (V400) = 0 00000 0000 0000 0000 0007 (V401) = 0 60000 0000 0000 0000 0005 (V402) = 1 00000 0000 0000 0000 0006 (V403) = 1 60000 0000 0000 0000 0007柦椷152541偑幚峴偝傟傞偲丅埲壓偺幚峴丄V5偺嵟弶偺4梫慺偑師偺抣偵側傞:

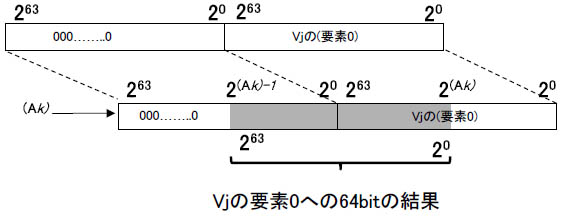

(V500) = 0 00000 0000 0000 0000 0073 (V501) = 0 00000 0000 0000 0000 0054 (V502) = 0 00000 0000 0000 0000 0067 (V503) = 0 00000 0000 0000 0000 0070柦椷153偼塃僔僼僩傪幚峴偡傞丅Vj偺奐巒梫慺0偼64bit偺0偲偮側偑傟偰丄 128bit偺検偲偟偰(Ak)偱巜掕偝傟偨偩偗塃僔僼僩偝傟傞丅寢壥偺壓埵64bit偑 Vi偺梫慺0偵憲傜傟傞丅恾5-10偑偙偺憖嶌傪恾夝偡傞丅

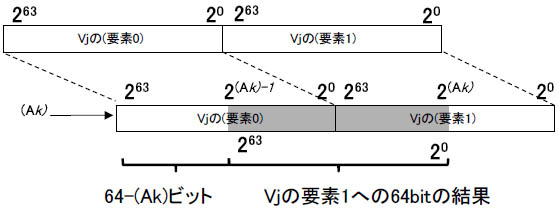

傕偟(VL)=1側傜丄偨偩1偮偺憖嶌偑幚峴偝傟傞丅堦斒偵丄梫慺0偲梫慺1偑偮側 偄偱柦椷幚峴偼宲懕偟丄128bit偺検偲偟偰(Ak)偱巜掕偝傟偨偩偗僔僼僩偟丄寢 壥偑丄Vj偺梫慺1偵憲傜傟傞丅恾5-11偑偙偺憖嶌傪恾夝偡傞丅

椺2. 傕偟柦椷153偑幚峴偝傟傞偲偟偰丄師偺儗僕僗僞忦審偑偁偭偨傜:

(VL) = 4 (A6) = 3 (V200) = 0 00000 0000 0000 0000 0017 (V201) = 0 60000 0000 0000 0000 0006 (V202) = 1 00000 0000 0000 0000 0006 (V203) = 1 60000 0000 0000 0000 0007柦椷153026偑幚峴偝傟傞偲丅 埲壓偺幚峴丄 V0偺嵟弶偺4梫慺偑師偺抣偵側傞:

(V000) = 0 00000 0000 0000 0000 0001 (V001) = 1 66000 0000 0000 0000 0000 (V002) = 1 50000 0000 0000 0000 0000 (V003) = 1 56000 0000 0000 0000 0000V0偺巆傝偺梫慺偼曄壔偟側偄丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 154 -157 | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷154偐傜157偼儀僋僩儖壛嶼婡擻儐僯僢僩偱幚峴偝傟傞丅

柦椷154偲155偼惍悢壛嶼傪峴偆丅柦椷156偲157偼惍悢尭嶼傪峴偆丅壛嶼傗尭嶼 偺幚峴偝傟傞屄悢偼丄VL儗僕僗僞偺撪梕偱寛掕偝傟傞丅偡傋偰偺憖嶌偼丄V儗 僕僗僞偺梫慺0偐傜巒傑傝丄奺憖嶌偑幚峴偝傟傞搙偵丄梫慺斣崋偼1僀儞僋儕儊 儞僩偝傟傞丅偡傋偰偺寢壥偼丄Vi偺梫慺偵憲傜傟傞丅僆乕僶乕僼儘乕偼専弌偝 傟側偄丅

柦椷154偲156偼丄(Sj)傪婡擻儐僯僢僩撪偵僐僺乕偟丄儀僋僩儖憖嶌偑姰椆偡傞 傑偱丄僆儁儔儞僪偺堦偮偲偟偰丄偦偺僐僺乕偑曐帩偝傟傞丅懠曽偺僆儁儔儞僪 偼Vk偺梫慺偱偁傞丅柦椷155偲157偱偼丄椉僆儁儔儞僪偲傕V儗僕僗僞偐傜摼傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 160 - 167 | |||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

柦椷160偐傜167偼丄晜摦彫悢揰忔嶼婡擻儐僯僢僩偱幚峴偝傟傞丅堦偮偺柦椷偵 傛傞憖嶌偺孞傝曉偟偼丄VL儗僕僗僞偺撪梕偱寛掕偝傟傞丅慡憖嶌偼丄V儗僕僗 僞偺梫慺0偐傜奐巒偟丄奺憖嶌偺恑峴偺搙偵丄梫慺斣崋偑1憹壛偡傞丅

僆儁儔儞僪偼丄晜摦彫悢揰宍幃偱偁傞偲憐掕偝傟傞丅柦椷160,162,164偲166偼 (Sj)偺僐僺乕傪婡擻儐僯僢僩撪偵憲傝丄憖嶌偑姰椆偡傞傑偱丄僆儁儔儞僪偺堦 偮偲偟偰僐僺乕傪曐帩偡傞丅偦傟偵傛偭偰丄Sj偼丄儀僋僩儖憖嶌偵塭嬁偡傞偙 偲側偔丄懄嵗偵抣傪曄峏偱偒傞丅懠曽偺僆儁儔儞僪偼丄Vk偺梫慺偱偁傞丅柦椷 161,163,165,167偱偼丄椉僆儁儔儞僪偲傕V儗僕僗僞偐傜摼傜傟傞丅

慡寢壥偼Vi偺梫慺偵憲傜傟傞丅傕偟丄偳偪傜偐偺僆儁儔儞僪偑惓婯壔偝傟偰偄 側偗傟偽丄愊偑惓婯壔偝傟偰偄傞偙偲偼曐徹偝傟側偄丅傕偟丄椉僆儁儔儞僪偲 傕惓婯壔偝傟偰偄側偗傟偽丄愊偼惓婯壔偝傟偰偄側偄偩傠偆丅

斖埻奜偺忦審偵偮偄偰偼丄4復偵婰弎偟偰偄傞丅

柦椷160偼Sj撪偺晜摦彫悢揰検偲Vk偺梫慺偺晜摦彫悢揰検偺愊傪庢傝丄Vi偵寢 壥傪擖傟傞丅

柦椷161偼Vj偲Vk偺梫慺偺晜摦彫悢揰検偺愊傪庢傝丄Vi偵寢壥傪擖傟傞丅

柦椷162偼Sj撪偺晜摦彫悢揰検偲Vk偺梫慺偺晜摦彫悢揰検偺敿惛搙偺娵傔傜傟 偨愊傪庢傝丄Vi偵寢壥傪擖傟傞丅寢壥偺梫慺偺壓埵19bit偼0偱偁傞丅

柦椷163偼Vj偲Vk偺梫慺偺晜摦彫悢揰検偺敿惛搙偺娵傔傜傟偨愊傪庢傝丄Vi偵 寢壥傪擖傟傞丅寢壥偺梫慺偺壓埵19bit偼0偱偁傞丅

柦椷164偼Sj撪偺晜摦彫悢揰検偲Vk偺梫慺偺晜摦彫悢揰検偺娵傔傜傟偨愊傪庢 傝丄Vi偵寢壥傪擖傟傞丅

柦椷165偼Vj偲Vk偺梫慺偺晜摦彫悢揰検偺娵傔傜傟偨愊傪庢傝丄Vi偵寢壥傪擖 傟傞丅

柦椷166偼丄奺梫慺偵偮偒丄Sj撪偺晜摦彫悢揰検偲Vk偺梫慺偺晜摦彫悢揰検偺 愊傪庢傝偦傟傪2偐傜尭偠傞丅寢壥偼Vi偵擖傟傞丅徻偟偔偼丄柦椷067偺婰弎傪 嶲徠丅

柦椷167偼丄奺梫慺偺慻偵偮偒丄Vj偲Vk偺梫慺偺晜摦彫悢揰検偺愊傪庢傝偦傟 傪2偐傜尭偠偰丄寢壥傪Vi偵擖傟傞丅徻偟偔偼丄柦椷067偺婰弎傪嶲徠丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 170 - 173 | |||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷170偐傜173偼晜摦彫悢揰壛嶼婡擻儐僯僢僩偱幚峴偝傟傞丅柦椷170偲171偼 晜摦彫悢揰偺壛嶼傪峴偆; 柦椷172偲173偼晜摦彫悢揰偺尭嶼傪峴偆丅堦偮偺柦 椷偵傛偭偰丄幚峴偝傟傞壛嶼偐尭嶼偺悢偼VL儗僕僗僞偺撪梕偵傛偭偰寛掕偝傟 傞丅偡傋偰偺憖嶌偼V儗僕僗僞偺梫慺0偐傜巒傑傝丄奺憖嶌偑幚峴偝傟傞搙偵丄 梫慺斣崋偼1僀儞僋儕儊儞僩偝傟傞丅Vi傊憲傜傟傞偡傋偰偺寢壥偼丄惓婯壔偝 傟傞丅傕偟僆儁儔儞僪偑惓婯壔偝傟偰偄側偐偭偨偲偟偰傕丄寢壥偼惓婯壔偝傟 傞丅

柦椷170偲172偼丄(Sj)偺僐僺乕傪婡擻儐僯僢僩撪偵憲傝丄憖嶌偑姰椆偡傞傑偱丄 僆儁儔儞僪偺堦偮偲偟偰僐僺乕傪曐帩偡傞丅懠曽偺僆儁儔儞僪偼丄Vk偺梫慺偱 偁傞丅柦椷171偲173偱偼丄椉僆儁儔儞僪偲傕V儗僕僗僞偐傜摼傜傟傞丅斖埻奜 偺忦審偵偮偄偰偼丄4復偵婰弎偟偰偄傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 174 | ||||||

|---|---|---|---|---|---|---|

|

柦椷174偼媡悢嬤帡婡擻儐僯僢僩偱幚峴偝傟傞丅柦椷偼Vj偺梫慺偺惓婯壔偝傟 偨晜摦彫悢揰検偺媡悢偺嬤帡抣傪嶌傝丄寢壥傪Vi偺梫慺偵擖傟傞丅嬤帡傪媮傔 傞梫慺偺悢偼丄VL儗僕僗僞偺撪梕偵傛偭偰寛掕偝傟傞丅

柦椷174偼丄4愡偺晜摦彫悢揰嶼弍墘嶼偵婰弎偝傟偰偄傞傛偆偵丄晜摦彫悢揰検 偺彜傪寁嶼偡傞彍嶼僔乕働儞僗偱巊傢傟傞丅

媡悢嬤帡柦椷偼忋埵30bit偺寢壥傪惗惉偡傞丅壓埵18bit偼0偱偁傞丅忋埵價僢 僩偼丄嬤帡孞傝曉偟柦椷偲忔嶼偵傛偭偰丄48bit偵奼挘偱偒傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審:

| 柦椷 174ij1 - 174ij2 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

|

柦椷174ij1偲174ij2偼儀僋僩儖丒億僺儏儗乕僔儑儞/僷儕僥傿婡擻儐僯僢僩偱 幚峴偝傟丄偄偔偮偐偺榑棟夞楬偑媡悢嬤帡婡擻儐僯僢僩偲嫟桳偝傟偰偄傞丅

柦椷174ij1偼Vj偺奺梫慺偺1偵僙僢僩偝傟偰偄傞價僢僩偺悢傪悢偊偰丄寢壥傪 Vi偺懳墳偡傞梫慺偵擖傟傞丅寢壥偼Vi偺奺梫慺偺壓埵7bit 偵擖傞丅Vi偺奺梫 慺偺巆傝偺忋埵價僢僩偵偼丄0偑擖傞丅

柦椷174ij2偼Vj偺奺梫慺偺1偵僙僢僩偝傟偰偄傞價僢僩偺悢傪悢偊傞丅奺梫慺 偺寢壥偺嵟壓埵價僢僩偑丄寢壥偑婏悢偐嬼悢偐傪昞偟偰偄傞丅奺梫慺偺嵟壓埵 價僢僩偩偗偑Vi偺懳墳偡傞梫慺偺嵟壓埵價僢僩埵抲偵揮憲偝傟傞丅梫慺偺巆傝 偺忋埵價僢僩偵偼丄0偑擖傞丅杮摉偺億僺儏儗乕僔儑儞丒僇僂儞僩偺寢壥偼揮 憲偝傟側偄丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

| 柦椷 175 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||

| (拲+: 摿庩CAL暥朄) |

儀僋僩儖丒儅僗僋柦椷175偼僼儖丒儀僋僩儖榑棟婡擻儐僯僢僩偱幚峴偝傟傞丅

柦椷1750jk偼丄Vj儗僕僗僞偺梫慺偺撪梕傪僥僗僩偟偨寢壥偵傛傝丄VM拞偵儀僋 僩儖丒儅僗僋傪惗惉偡傞丅VM偺奺價僢僩偼丄Vj偺梫慺偵懳墳偡傞丅價僢僩2^63 偼梫慺0偵懳墳偟; 價僢僩2^0偼梫慺63偵懳墳偡傞丅

柦椷偵傛偭偰峴傢傟傞僥僗僩偺宆偼丄k巜掕巕偺壓埵2bit偵傛傞丅k巜掕巕偺忋 埵價僢僩偼巊傢傟側偄丅

傕偟k巜掕巕偑0側傜丄(Vj偺梫慺)偑0側傜VM價僢僩偼1偵丄(Vj偺梫慺)偑旕0側 傜VM價僢僩偼0偵丄僙僢僩偝傟傞丅

傕偟k巜掕巕偑1側傜丄(Vj偺梫慺)偑旕0側傜VM價僢僩偼1偵丄(Vj偺梫慺)偑0側 傜VM價僢僩偼0偵丄僙僢僩偝傟傞丅

傕偟k巜掕巕偑2側傜丄(Vj偺梫慺)偑惓側傜VM價僢僩偼1偵丄(Vj偺梫慺)偑晧側 傜VM價僢僩偼0偵丄僙僢僩偝傟傞丅0偼惓偲偡傞丅

傕偟k巜掕巕偑3側傜丄(Vj偺梫慺)偑晧側傜VM價僢僩偼1偵丄(Vj偺梫慺)偑惓側 傜VM價僢僩偼0偵丄僙僢僩偝傟傞丅0偼惓偲偡傞丅

僥僗僩偝傟傞梫慺偺悢偼VL儗僕僗僞偺撪梕偵傛偭偰寛掕偝傟傞丅僥僗僩偝傟側 偄Vj偺梫慺偵懳墳偡傞VM價僢僩偼0偵偝傟傞丅

儀僋僩儖丒儅僗僋柦椷175偼丄儀僋僩儖偵偍偗傞僗僇儔偺忦審暘婒柦椷偵懳墳 偡傞傕偺傪採嫙偡傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

(拲++: 儀僋僩儖柦椷偼懄嵗偵幚峴奐巒偟偨傝丄偟側偐偭偨傝偡傞; 僨乕僞偑 棙梡壜擻偵側偭偨帪偵幚峴偡傞丅摿偵丄儀僋僩儖偺偄偔偮偐偺梫慺偺儘乕僪偺 幚峴傪抶偔偡傞儊儌儕嫞崌偼丄儘乕僪偐傜巒傑傞僆儁儗乕僔儑儞丒僠僃僀儞偺 偡傋偰偺柦椷偺抶墑傪堷偒婲偙偡偙偲偑偁傞丅)

摿庩忦審:

| 柦椷 176 - 177 | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||

| (拲+: 摿庩CAL暥朄) |

柦椷176偲177偼V儗僕僗僞偲儊儌儕偺娫偱丄僨乕僞偺僽儘僢僋揮憲傪峴偆丅

柦椷176偼僨乕僞傪儊儌儕偐傜丄儗僕僗僞Vi偺梫慺偵揮憲偡傞丅

柦椷177偼僨乕僞傪儗僕僗僞Vi偺梫慺偐傜丄儊儌儕傊揮憲偡傞丅

儗僕僗僞梫慺偼0偐傜巒傑傝丄揮憲偛偲偵1偯偮憹偊傞丅儊儌儕斣抧偼(A0)偐傜 巒傑傝丄Ak偺撪梕偩偗憹壛偡傞丅Ak偼晞崋晅22bit惍悢傪曐帩偟丄師偺儚乕僪 偺傾僪儗僗傪摼傞偨傔偵丄尰嵼偺儚乕僪偺傾僪儗僗偵壛嶼偝傟傞丅(Ak)偺忋埵 2bit偼柍帇偝傟傞丅Ak偼惓悢傕晧悢傕憹暘偵巜掕偱偒丄儊儌儕嶲徠偺棳傟偼慜 岦偒傕屻傠岦偒傕嫋偝傟傞丅

揮憲偝傟傞儚乕僪偺悢偼VL儗僕僗僞偺撪梕偱寛掕偝傟傞丅

儂乕儖僪敪峴忦審:

幚峴帪娫:

摿庩忦審: